# ABOV SEMICONDUCTOR 8-BIT SINGLE-CHIP MICROCONTROLLERS

# MC81F4x32

MC81F4332 M/G/D/K MC81F4432 K/Q

User's Manual (Ver. 1.35)

Version 1.35

Published by FAE Team

©2008 ABOV Semiconductor Co., Ltd. All rights reserved.

Additional information of this manual may be served by ABOV Semiconductor offices in Korea or Distributors.

ABOV Semiconductor reserves the right to make changes to any information here in at any time without notice.

The information, diagrams and other data in this manual are correct and reliable; however, ABOV Semiconductor is in no way responsible for any violations of patents or other rights of the third party generated by the use of this manual.

2

#### **REVISION HISTORY**

#### VERSION 1.34 (October 19, 2009) This book

Add a note about SCK port at R0CONM register description.

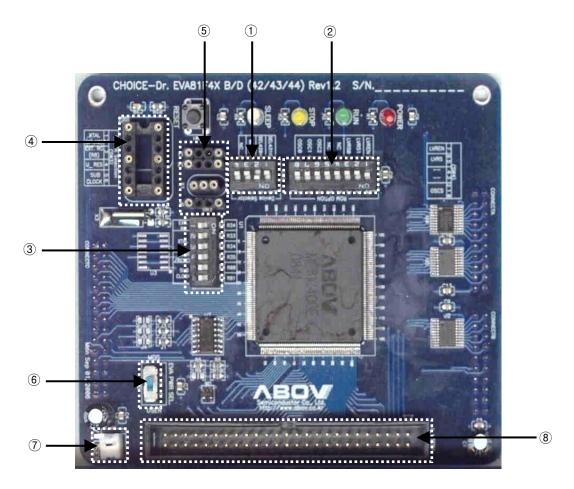

Change EVA.board picture. (the board's color is changed from blue to green)

## **VERSION 1.34 (September 30, 2009)**

Correct the duty equation of PMW0/1.

Add more tools at "1.3 Development Tools".

#### **VERSION 1.33 (September 18, 2009)**

Add more descriptions at PWM function descriptions.

#### **VERSION 1.32 (September 4, 2009)**

Remove rising/falling time at LVR electrical characteristics.

Change '1.83v' to "POR level" in POR description.

Add POR level at "DC CHARACTERISTICS".

The package diagram of 44 MQFP is corrected.

Add ROM option read timing information.

Add "Typical Characteristics".

## **VERSION 1.21 (July 7, 2009)**

"Figure 25-5 IIC Salve Receiving Timing Diagram" is modified.

"29.3 Hardware Conditions to Enter the ISP Mode" is updated.

Notes of R35 port control registers are updated.

#### **VERSION 1.2 (June 29, 2009)**

Change the representative name from 'MC81F4432' to 'MC81F4x32'.

Remove 'WDT' at "Stop release" description. 'WDT' is not a release source of STOP mode.

Add 'Watch Timer' at stop release source at "Peripheral Operation During Power Saving Mode" table in "Sleep vs Stop" chapter.

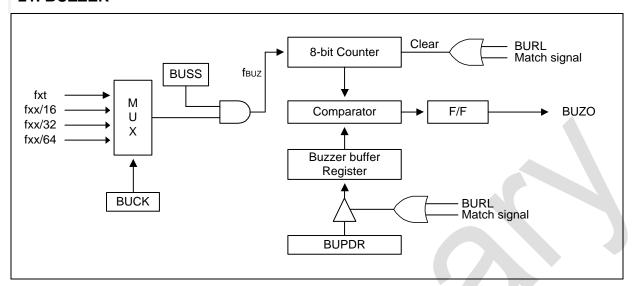

Change "fxin" to "fbuz" at buzzer frequency calculation in "BUZZER" chapter.

#### **VERSION 1.1 (June 15, 2009)**

Add rom writing endurance at features.

## **VERSION 1.0 (June 15, 2009)**

Remove "preliminary".

Some errata are fixed. (I2C -> IIC, IICSDR->IICSCR)

Remove "R57, R56, R55, R54" in R5 port data register table.

Add "Buzzer frequency table".

#### VERSION 0.61 Preliminary (April 28, 2009)

Delete a note1 at '22.5 recommended circuit'

#### VERSION 0.6 Preliminary (April 16, 2009)

Add a sub-chapter 'Changing the stabilizing time' at the chapter 'Power down operation'. Add a note for R33/R34 ports after R3CONH description.

One of BIT's clock source '2048' is changed to '1024'.

## VERSION 0.5 Preliminary (April 7, 2009)

Description of SIO procedure is updated.

Description of ISP chapter is updated.

#### **VERSION 0.4 Preliminary (April 1, 2009)**

Chapter '7.ELECTRICAL CHARACTERISTICS' is updated.

#### VERSION 0.3 Preliminary (March 19, 2009)

The SCLK pin for ISP is moved to R11 port.

#### **VERSION 0.2 Preliminary (March 5, 2009)**

The SCLK pin for ISP is moved to R14 port.

Note for ADC recommended circuit is changed.

Change 44MQFP package diagram.

#### **VERSION 0.1 Preliminary (February 12, 2009)**

Update the chapter '6. PORT STRUCTURE'.

Update the chapter '7. ELECTRICAL CHARACTERISTICS'.

Update the chapter '29. IN SYSTEM PROGRAMMING'.

#### **VERSION 0.0 Preliminary (December 19, 2008)**

# **TABLE OF CONTENTS**

| REVISION HISTORY                                       | 3  |

|--------------------------------------------------------|----|

| TABLE OF CONTENTS                                      | 5  |

| 1. OVERVIEW                                            | 9  |

| 1.1 Description                                        | 9  |

| 1.2 Features                                           | 9  |

| 1.3 Development Tools                                  | 10 |

| 1.4 Ordering Information                               | 11 |

| 2. BLOCK DIAGRAM                                       | 12 |

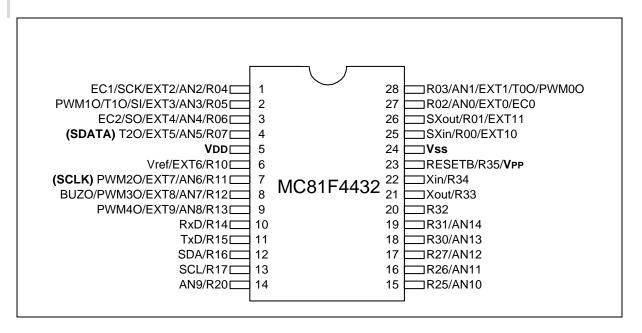

| 3. PIN ASSIGNMENT                                      | 13 |

| 3.1 44 MQFP                                            | 13 |

| 3.2 42 SDIP                                            | 14 |

| 3.3 32 SDIP/SOP                                        | 14 |

| 3.4 28 SKDIP/SOP                                       | 15 |

| 3.5 Summary                                            | 16 |

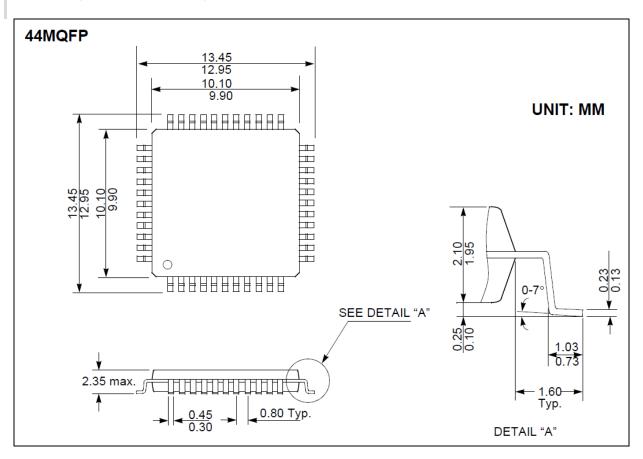

| 4. PACKAGE DIAGRAM                                     |    |

| 4.1 44 MQFP - MC81F4432Q                               | 18 |

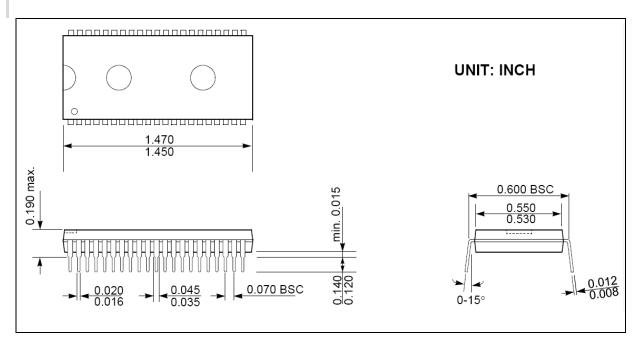

| 4.2 42 SDIP - MC81F4432K                               | _  |

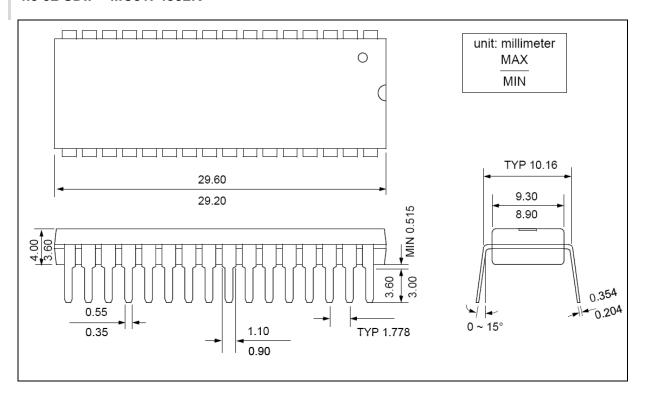

| 4.3 32 SDIP - MC81F4332K                               | 19 |

| 4.4 32 SOP - MC81F4332D                                | 19 |

| 4.5 28 SKDIP - MC81F4332G                              | 20 |

| 4.6 28 SOP - MC81F4332M                                | 20 |

| 5. PIN DESCRIPTION                                     | 21 |

| 6. PORT STRUCTURE                                      |    |

| 7. ELECTRICAL CHARACTERISTICS                          | 29 |

| 7.1 Absolute Maximum Ratings                           |    |

| 7.2 RECOMMENDED OPERATING CONDITION                    |    |

| 7.3 A/D CONVERTER CHARACTERISTICS)                     |    |

| 7.4 DC CHARACTERISTICS                                 | 31 |

| 7.5 DC CHARACTERISTICS(continued)                      |    |

| 7.6 Input/output Capacitance                           | 32 |

| 7.7 Serial I/O Characteristics                         |    |

| 7.8 Data Retention Voltage in Stop Mode                | 34 |

| 7.9 LVR (Low Voltage Reset) Electrical Characteristics | 36 |

| 7.10 UART Timing Characteristics                       | 36 |

| 7.11 IIC Timing Characteristics                        |    |

| 7.12 Main clock Oscillator Characteristics             | 39 |

| 7.13 External RC Oscillation Characteristics           | 39 |

| 7.14 Internal RC Oscillation Characteristics           | 40 |

| 7.15 Sub clock Oscillator Characteristics              | 40 |

| 7.16 Main Oscillation Stabilization Time               | 40 |

| 7.17 Sub Oscillation Stabilization Time                | 41 |

| 7.18 Operating Voltage Range                           | 42 |

| 7.19 Typical Characteristics                           |    |

| 8. ROM OPTION                                          |    |

| 8.1 Rom Option                                         | 47 |

| 8.2 Read Timing                        | 48  |

|----------------------------------------|-----|

| 9. MEMORY ORGANIZATION                 | 49  |

| 9.1 Registers                          | 49  |

| 9.2 Program Memory                     | 52  |

| 9.3 Data Memory                        | 55  |

| 9.4 User Memory                        | 55  |

| 9.5 Stack Area                         | 56  |

| 9.6 Control Registers ( SFR )          | 56  |

| 9.7 Addressing modes                   | 61  |

| 10. I/O PORTS                          | 68  |

| 10.1 R0 Port Registers                 | 70  |

| 10.2 R1 Port Registers                 | 74  |

| 10.3 R2 Port Registers                 | 78  |

| 10.4 R3 Port Registers                 | 81  |

| 10.5 R4 Port Registers                 | 83  |

| 10.6 R5 Port                           | 85  |

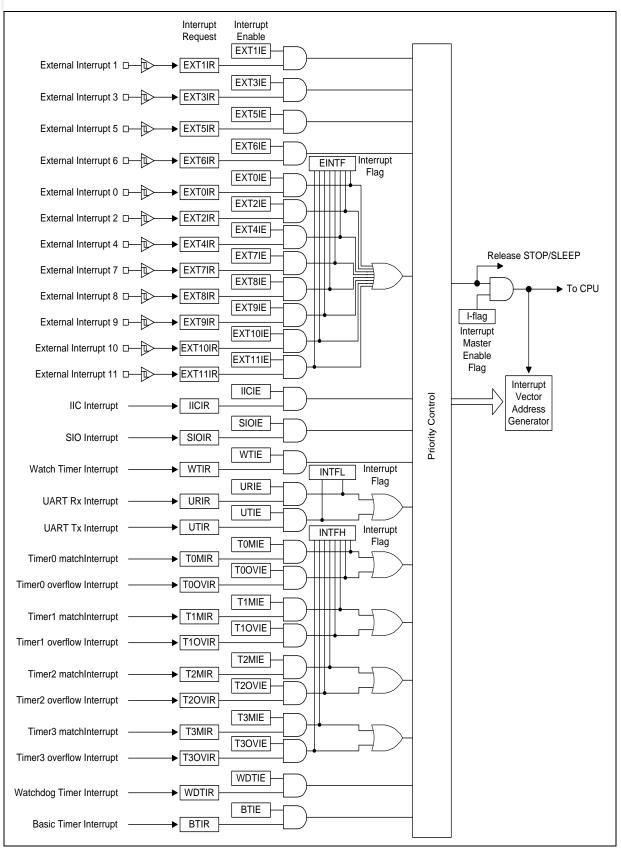

| 11. INTERRUTP CONTROLLER               | 86  |

| 11.1 Registers                         | 87  |

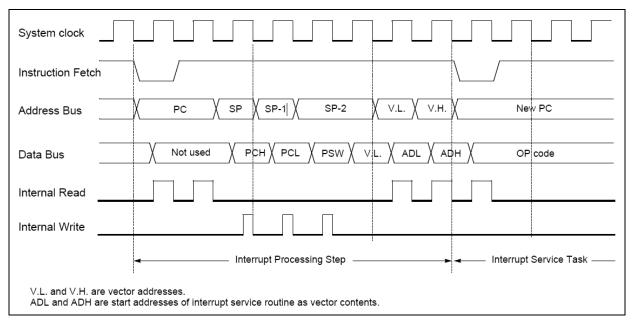

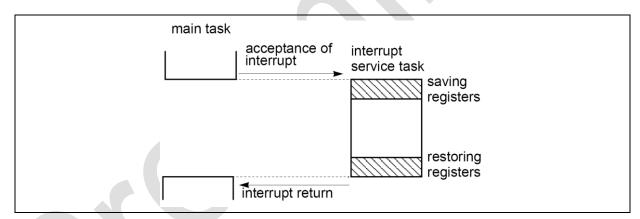

| 11.2 Interrupt Sequence                | 92  |

| 11.3 BRK Interrupt                     | 94  |

| 11.4 Shared Interrupt Vector           | 94  |

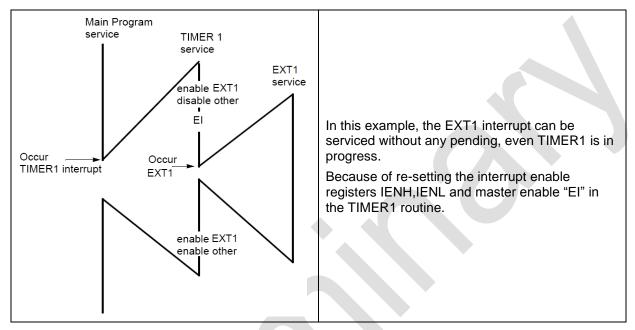

| 11.5 Multi Interrupt                   | 95  |

| 11.6 Interrupt Vector & Priority Table | 96  |

| 12. EXTERNAL INTERRUPTS                |     |

| 12.1 Registers                         | 97  |

| 12.2 Procedure                         | 100 |

| 13. CLOCK GENERATOR                    | 101 |

| 13.1 Registers                         | 102 |

| 14. OSCILLATION CIRCUITS               | 103 |

| 14.1 Main Oscillation Circuits         | 103 |

| 14.2 Sub Oscillation Circuits          | 104 |

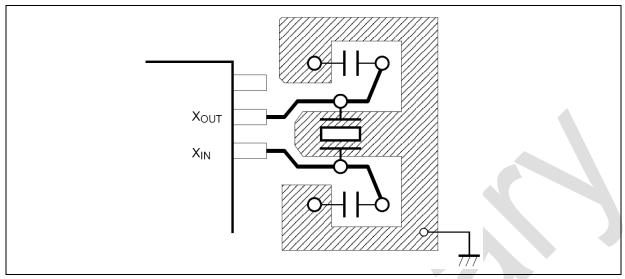

| 14.3 PCB Layout                        | 105 |

| 15. BASIC INTERVAL TIMER               | 106 |

| 15.1 Registers                         | 107 |

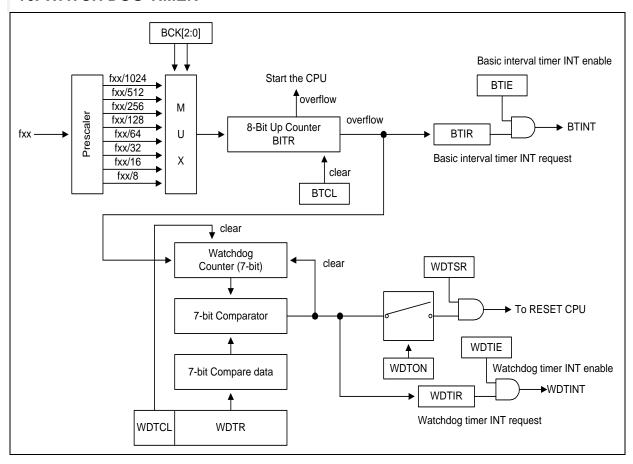

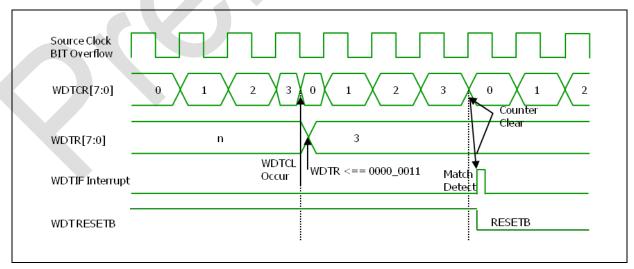

| 16. WATCH DOG TIMER                    | 108 |

| 16.1 Registers                         | 109 |

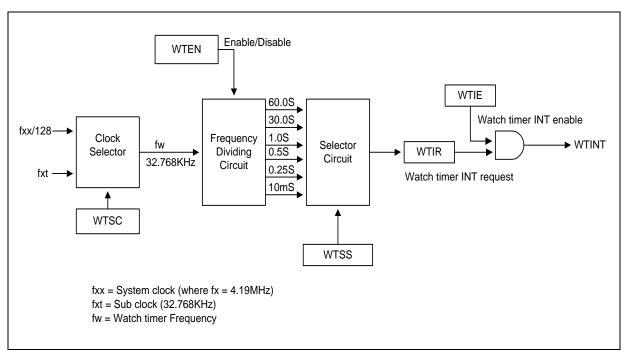

| 17. WATCH TIMER                        | 110 |

| 17.1 Registers                         | 111 |

| 18. Timer 0/1                          | 112 |

| 18.1 Registers                         | 112 |

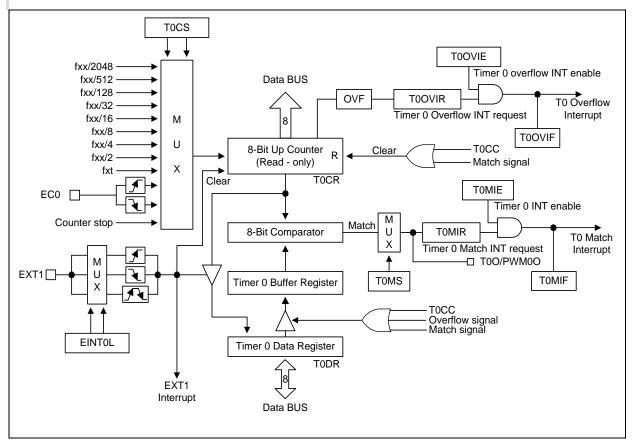

| 18.2 Timer 0 8-Bit Mode                | 116 |

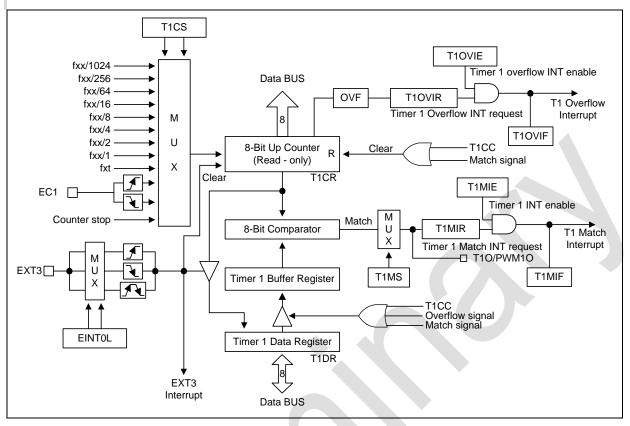

| 18.3 Timer 1 8-Bit Mode                | 119 |

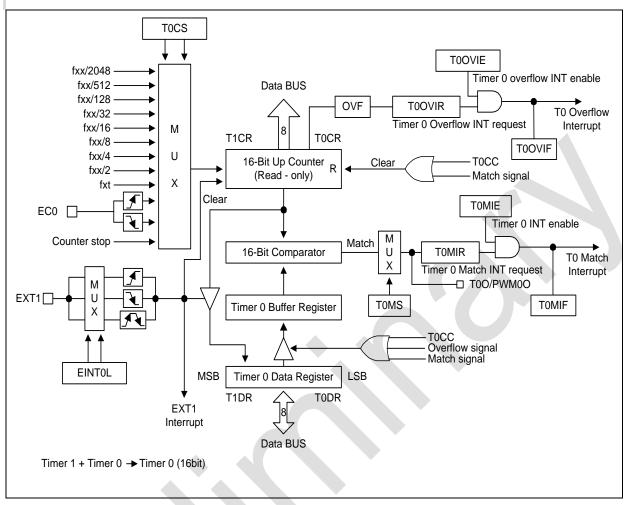

| 18.4 Timer 0 16-BIT Mode               | 121 |

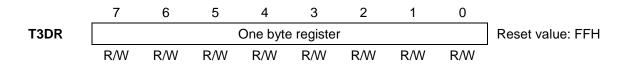

| 19. Timer 2/3                          | 124 |

| 19.1 Registers                         | 124 |

| 19.2 Timer 2 8-Bit Mode                | 129 |

| 19.3 Timer 3 8-Bit Mode                | 131 |

| 19.4 Timer 2 16-Bit Mode               | 133 |

| 20. High Speed PWM                             | 135 |

|------------------------------------------------|-----|

| 20.1 Registers                                 | 137 |

| 21. BUZZER                                     | 139 |

| 21.1 Registers                                 | 140 |

| 21.2 Frequency table                           | 141 |

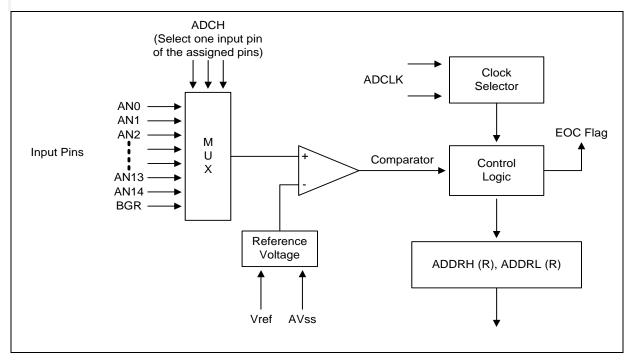

| 22. 12-BIT ADC                                 | 142 |

| 22.1 Registers                                 | 143 |

| 22.2 Procedure                                 | 144 |

| 22.3 Conversion Timing                         | 144 |

| 22.4 Internal Reference Voltage                | 145 |

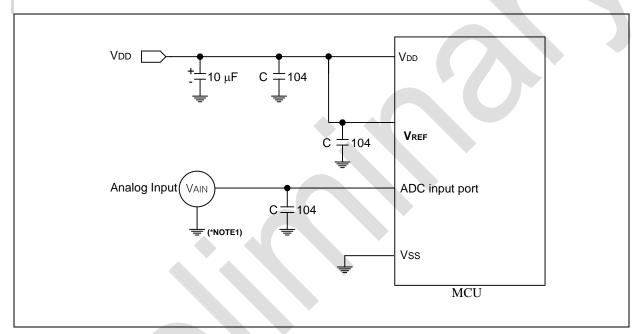

| 22.5 Recommended Circuit                       | 145 |

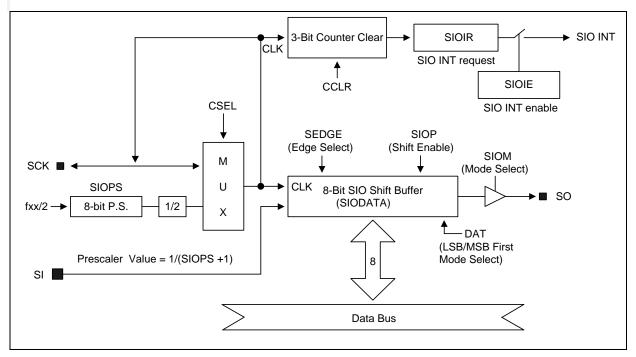

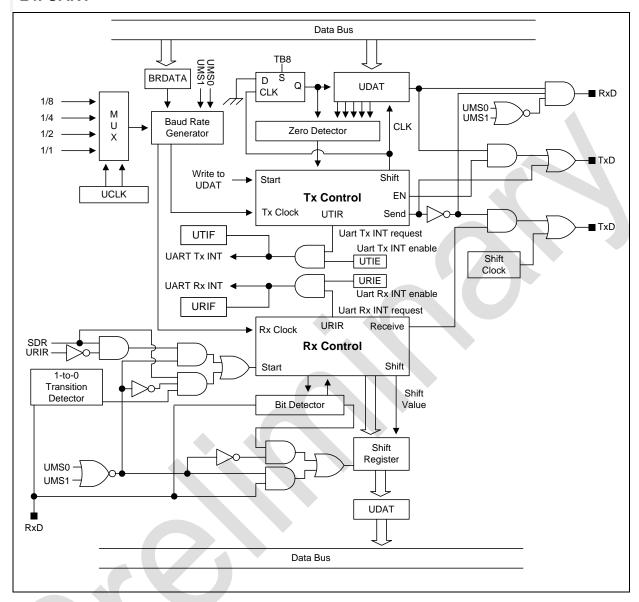

| 23. SERIAL I/O INTERFACE                       | 146 |

| 23.1 Registers                                 | 147 |

| 23.2 Procedure                                 | 148 |

| 24. UART                                       | 149 |

| 24.1 Registers                                 | 150 |

| 24.2 Modes and Procedures                      |     |

| 24.3 Baud rate calculations                    |     |

| 24.4 Muti-processor Communication              |     |

| 24.5 Interrupt                                 |     |

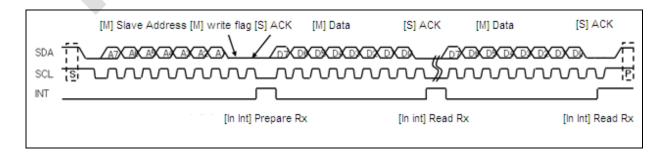

| 25. SLAVE IIC                                  |     |

| 25.1 Roles                                     |     |

| 25.2 Registers                                 |     |

| 25.3 Message format                            |     |

| 25.4 Procedure                                 |     |

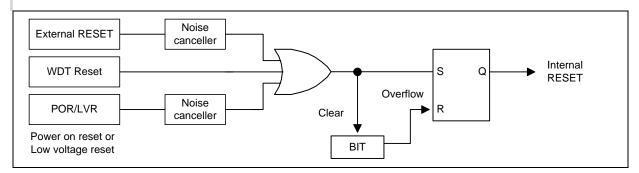

| 26. RESET                                      |     |

| 26.1 Reset Process                             |     |

| 26.2 Reset Sources                             |     |

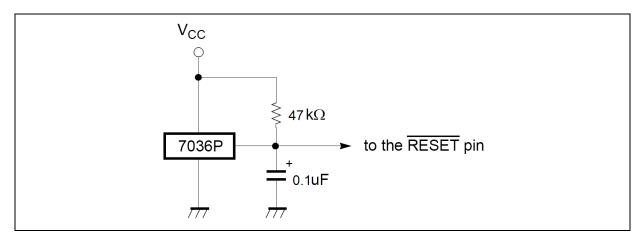

| 26.3 External Reset                            |     |

| 26.4 Watch Dog Timer Reset                     |     |

| •                                              |     |

| 26.5 Power On Reset                            |     |

| 26.6 Low Voltage Reset                         |     |

| 27. POWER DOWN OPERATION                       |     |

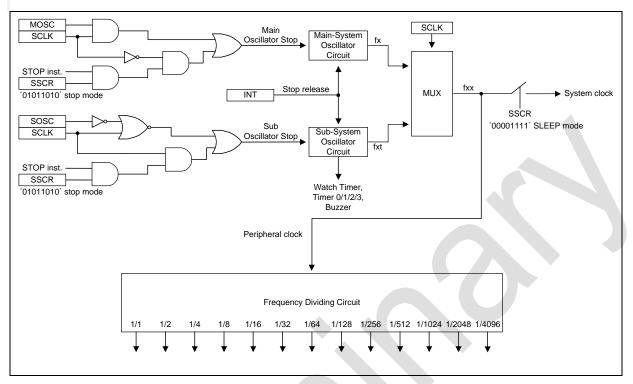

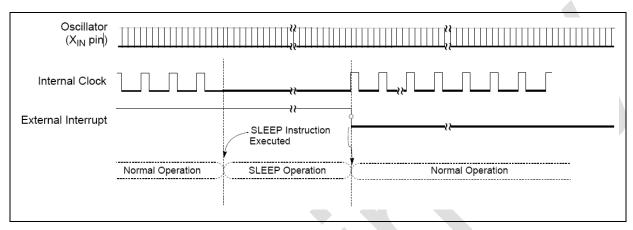

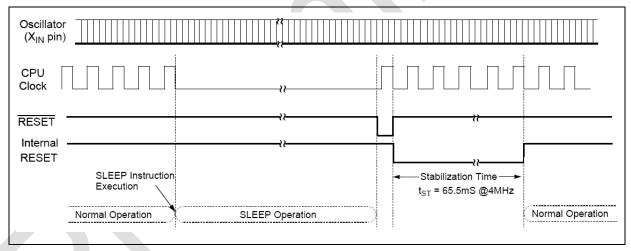

| 27.1 Sleep Mode                                |     |

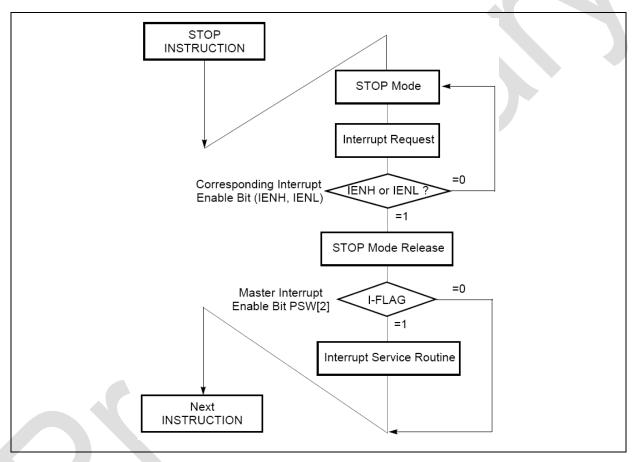

| 27.2 Stop Mode                                 |     |

| 27.3 Sleep vs Stop                             |     |

| 27.4 Changing the stabilizing time             |     |

| 27.5 Minimizing Current Consumption            |     |

| 28. EMULATOR                                   |     |

| 29. IN SYSTEM PROGRAMMING                      |     |

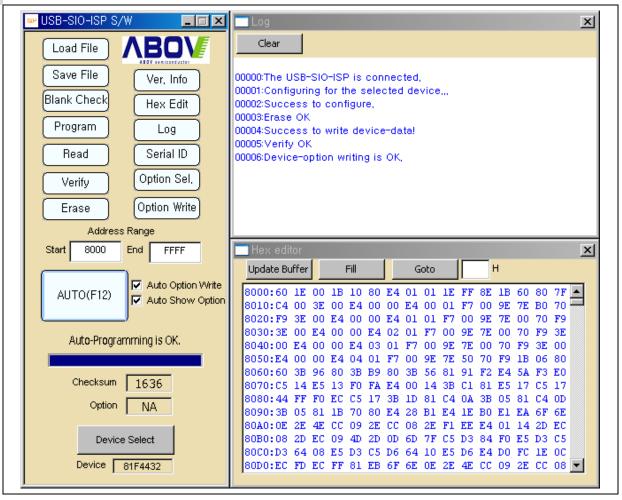

| 29.1 Getting Started                           |     |

| 29.2 Basic ISP S/W Information                 |     |

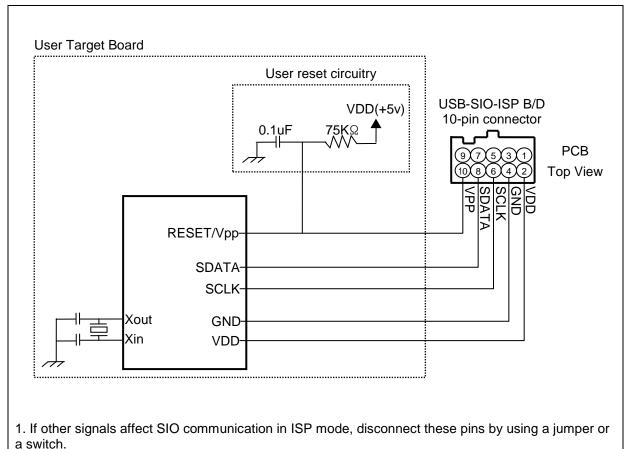

| 29.3 Hardware Conditions to Enter the ISP Mode |     |

| 29.4 Entering ISP mode at power on time        |     |

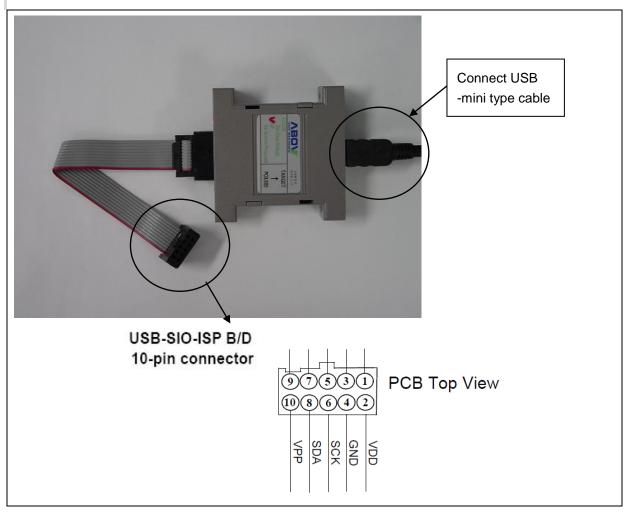

| 29.5 USB-SIO-ISP Board                         | 186 |

| 30. INSTRUCTION SET                            | 187 |

| 30.1 Terminology List                          | 187 |

| 30.2 Instruction Map                           | 188 |

| MC81F4x32  | ∧BO <b>V</b>   |

|------------|----------------|

| WIC81F4X32 | ∧BU <b>V</b> € |

# MC81F4x32

# 8 bit MCU with 12-bit A/D Converter

#### 1. OVERVIEW

## 1.1 Description

MC81F4x32 is a CMOS 8 bit MCU which provides a 32K bytes FLASH-ROM and 512 bytes RAM. It has following major features,

12 bit ADC: It has 15 ch A/D Converter which can be used to measure minute electronic voltage and currents.

810 Core : Same with ABOV's 800 Core but twice faster. 800 Core use a divided system clock but 810 Core use a system clock directly

Power Consumption – Sub Active Mode: To decrease the power consumption, It can be operated with sub clock( 32.768KHz ).

#### 1.2 Features

ROM (FLASH): 32K Bytes

(Endurance: 100 cycle)

SRAM : 1K Bytes

#### **Minimum Instruction Execution Time**

166nsec (@12MHz 2 Cycle NOP Instruction)

#### Power down mode

IDLE, STOP, SLEEP mode

Sub-Active mode

(Operates at 32.768KHz sub clock)

#### **General Purpose I/O (GPIO)**

44-pin PKG: 42 ports 42-pin PKG: 40 ports 32-pin PKG: 30 ports 28-pin PKG: 26 ports

SIO: 1ch

Uart: 1ch

IIC slave: 1ch

Timer/ Counter

8Bit × 4ch (or 16Bit x 2ch)

#### **PWM**

(8Bit x 2ch or 16Bit x 1ch) + 10Bit x 3ch

Buzzer : 1ch ( 244 ~ 250KHz @8MHz )

Watch Timer (WT) : 8Bit x 1ch

Basic Interval Timer (BIT) : 8Bit x 1ch

Watch Dog Timer (WDT) : 8Bit x 1ch

October 19, 2009 Ver.1.35

12 Bit A/D Converter: 15 ch

Interrupt Sources : 27ch

External interrupts(EXT0~11) : 12ch

Timer0~3 Match/overflow : 8ch

WDT, BIT, WT : 3ch

SIO,UART(Tx/Rx), IIC : 4ch

#### Power On Reset (POR)

Reset release level (detect only rising)

## Low Voltage Reset (LVR)

4 level detector (4.0V, 3.0V, 2.7V, 2.4V)

#### **Operating Voltage & Frequency**

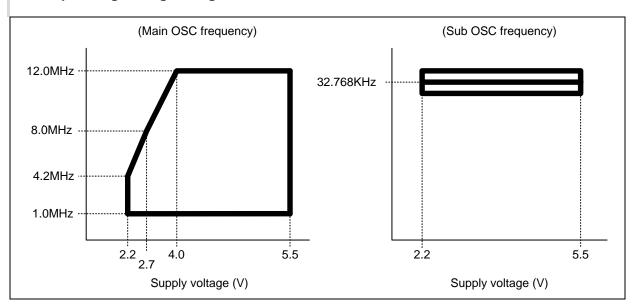

2.2V - 5.5V : 1.0 - 4.2 MHz 2.7V - 5.5V : 1.0 - 8.0 MHz 4.0V - 5.5V : 1.0 - 12.0 MHz

#### **Operating Temperature**

- 40°C ~ 85°C

# **Oscillator Type**

Crystal, Ceramic, RC

On-Chip RC-Oscillator (8/4/2/1MHz)

## **PKG Type**

44MQFP, 42SDIP, 32SDIP/SOP,

28 SKDIP/SOP

## 1.3 Development Tools

The MC81F4x32 is supported by a full-featured macro assembler, C-Compiler, an in-circuit emulator CHOICE-Dr. FALSH programmers and ISP tools. There are two different type of programmers such as single type and gang type. For more detail, Macro assembler operates under the MS-Windows 95 and up versioned Windows OS. And HMS800C compiler only operates under the MS-Windows 2000 and up versioned Windows OS.

Please contact sales part of ABOV semiconductor. And you can see more information at ( http://www.abov.co.kr )

Figure 1-1 PGMplusUSB (Single Writer)

Figure 1-2 SIO ISP (In System Programmer)

Figure 1-3 StandAlone ISP (VDD power is not supplied)

Figure 1-4 Ez-ISP (VDD supplied Standalone type ISP)

Figure 1-5 StandAlone Gang4 (for Mass Production)

Figure 1-6 StandAlone Gang8 (for Mass Production)

Figure 1-7 Choice-Dr (Emulator)

# 1.4 Ordering Information

| Device Name | FLASH ROM | RAM        | Package  |

|-------------|-----------|------------|----------|

| MC81F4332M  |           |            | 28_SOP   |

| MC81F4332G  |           |            | 28_SKDIP |

| MC81F4332D  | 32K Bytes | E40 Distan | 32_SOP   |

| MC81F4332K  |           | 512 Bytes  | 32_SDIP  |

| MC81F4432K  |           |            | 42_SDIP  |

| MC81F4432Q  |           |            | 44_MQFP  |

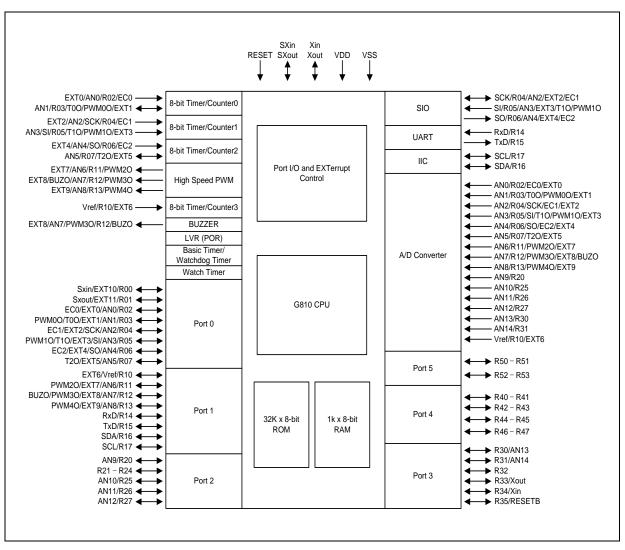

#### 2. BLOCK DIAGRAM

Figure 2-1 System Block Diagram

## 3. PIN ASSIGNMENT

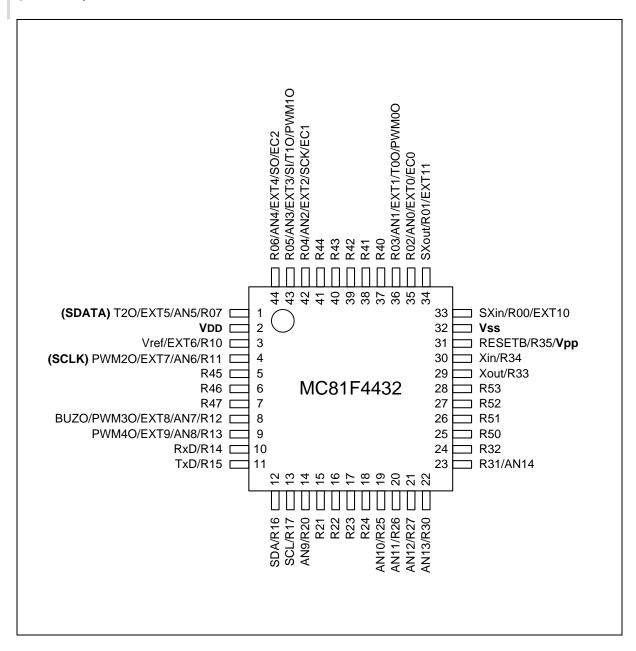

# 3.1 44 MQFP

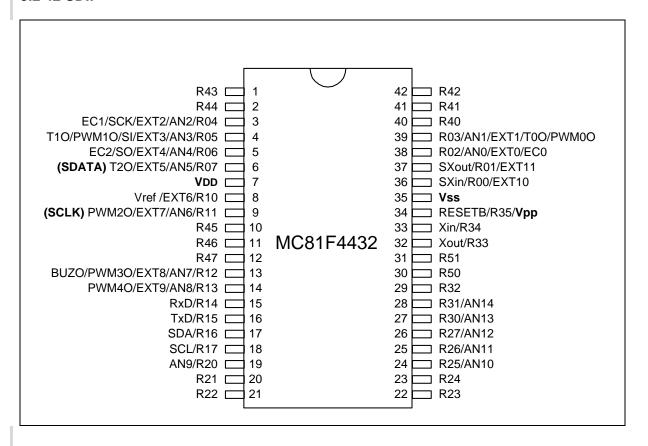

#### 3.2 42 SDIP

# 3.3 32 SDIP/SOP

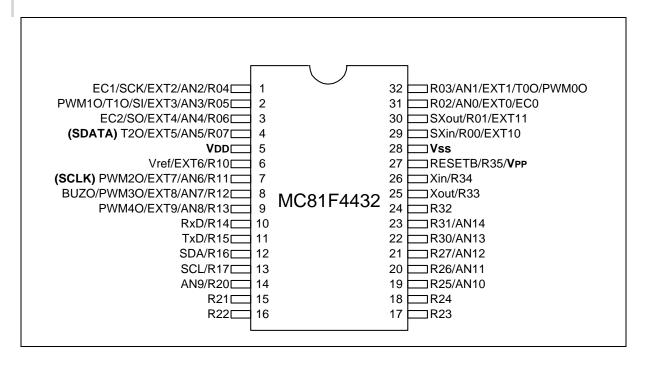

## **3.4 28 SKDIP/SOP**

# 3.5 Summary

| 1/0 | Pin number            |       |       |       |       | Pin status        |

|-----|-----------------------|-------|-------|-------|-------|-------------------|

| I/O | Alternative functions | 44pin | 42pin | 32pin | 28pin | at RESET          |

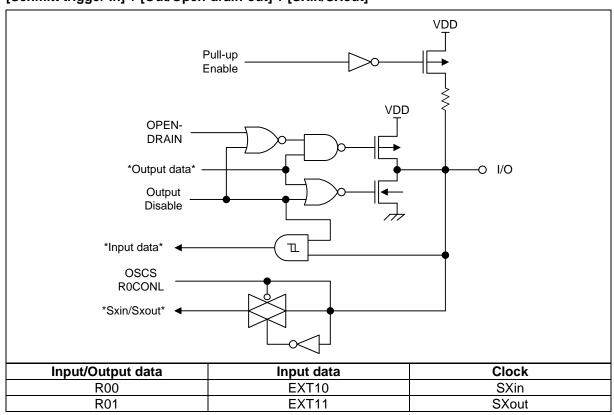

| R00 | EXT10/SXin            | 33    | 36    | 29    | 25    | input             |

| R01 | EXT11/SXout           | 34    | 37    | 30    | 26    | input             |

| R02 | AN0/EXT0/EC0/         | 35    | 38    | 31    | 27    | input             |

| R03 | AN1/EXT1/T0O/PWM0O    | 36    | 39    | 32    | 28    | input             |

| R04 | AN2/EXT2/EC1/SCK      | 42    | 3     | 1     | 1     | input             |

| R05 | AN3/EXT3/SI/T1O/PWM1O | 43    | 4     | 2     | 2     | input             |

| R06 | AN4/EXT4/EC2/SO       | 44    | 5     | 3     | 3     | input             |

| R07 | AN5/EXT5/T2O          | 1     | 6     | 4     | 4     | input             |

| R10 | Vref/EXT6             | 3     | 8     | 6     | 6     | input             |

| R11 | AN6/EXT7/PWM2O        | 4     | 9     | 7     | 7     | input             |

| R12 | AN7/EXT8/PWM3O/BUZO   | 8     | 13    | 8     | 8     | input             |

| R13 | AN8/EXT9/PWM4O        | 9     | 14    | 9     | 9     | Open-drain output |

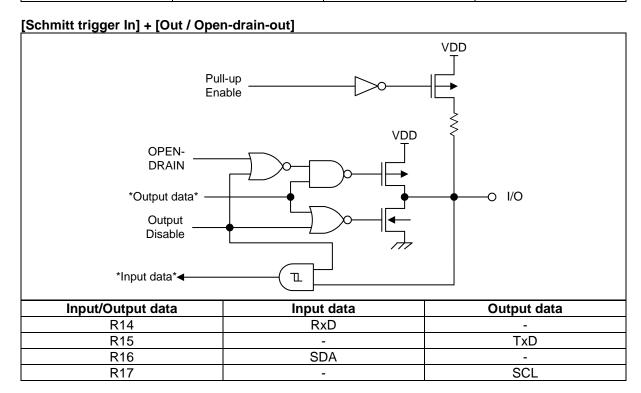

| R14 | RxD                   | 10    | 15    | 10    | 10    | Open-drain output |

| R15 | TxD                   | 11    | 16    | 11    | 11    | Open-drain output |

| R16 | SDA                   | 12    | 17    | 12    | 12    | Open-drain output |

| R17 | SCL                   | 13    | 18    | 13    | 13    | Open-drain output |

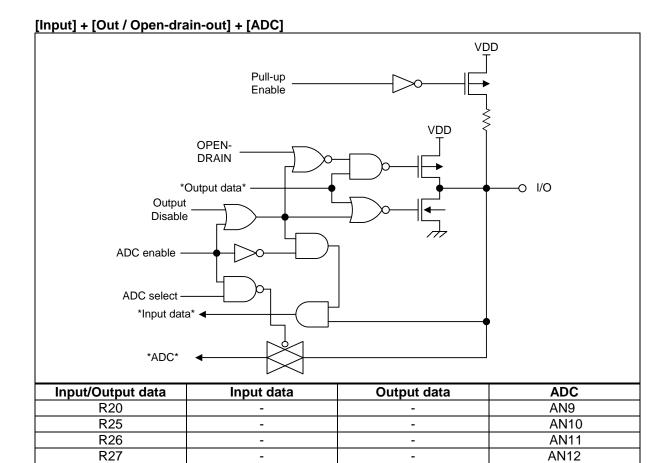

| R20 | AN9                   | 14    | 19    | 14    | 14    | Open-drain output |

| R21 | -                     | 15    | 20    | 15    | Х     | Open-drain output |

| R22 | -                     | 16    | 21    | 16    | Х     | Open-drain output |

| R23 | -                     | 17    | 22    | 17    | Х     | Open-drain output |

| R24 | -                     | 18    | 23    | 18    | Х     | Open-drain output |

| R25 | AN10                  | 19    | 24    | 19    | 15    | Open-drain output |

| R26 | AN11                  | 20    | 25    | 20    | 16    | Open-drain output |

| R27 | AN12                  | 21    | 26    | 21    | 17    | Open-drain output |

| R30 | AN13                  | 22    | 27    | 22    | 18    | Open-drain output |

| R31 | AN14                  | 23    | 28    | 23    | 19    | Open-drain output |

| R32 | -                     | 24    | 29    | 24    | 20    | Open-drain output |

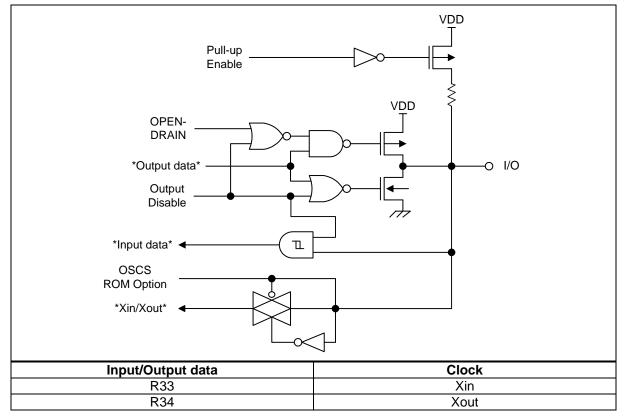

| R33 | Xout                  | 29    | 32    | 25    | 21    | input             |

| R34 | Xin                   | 30    | 33    | 26    | 22    | input             |

| R35 | RESETB                | 31    | 34    | 27    | 23    | input             |

| 1/0 | Alta mantina finantina |    | Pin nu | ımber |       | Pin status        |  |

|-----|------------------------|----|--------|-------|-------|-------------------|--|

| I/O | Alternative functions  |    |        | 32pin | 28pin | at RESET          |  |

| R40 | -                      | 37 | 40     | Х     | х     | Open-drain output |  |

| R41 | -                      | 38 | 41     | х     | х     | Open-drain output |  |

| R42 | -                      | 39 | 42     | Х     | х     | Open-drain output |  |

| R43 | -                      | 40 | 1      | х     | х     | Open-drain output |  |

| R44 | -                      | 41 | 2      | х     | х     | Open-drain output |  |

| R45 | -                      | 5  | 10     | х     | х     | Open-drain output |  |

| R46 | -                      | 6  | 11     | х     | х     | Open-drain output |  |

| R47 | -                      | 7  | 12     | х     | х     | Open-drain output |  |

| R50 | -                      | 25 | 30     | х     | х     | Open-drain output |  |

| R51 | -                      | 26 | 31     | Х     | х     | Open-drain output |  |

| R52 | -                      | 27 | х      | х     | х     | Open-drain output |  |

| R53 | -                      | 28 | х      | х     | х     | Open-drain output |  |

| VDD | -                      | 2  | 7      | 5     | 5     | -                 |  |

| VSS | -                      | 32 | 35     | 28    | 24    | -                 |  |

#### Note:

Some pins are initialized by open-drain output mode, when the device is reset. Because the pins are hided in 16 pin package and it is stable that hided pins are be in open-drain-output mode.

The reset status of MC81F4x32 is designed under consideration of 16 pin package of MC81F4204. Because MC81F4204 is a reduced version of MC81F4x32. (So the Eva.board(emulator) is shared)

# 4. PACKAGE DIAGRAM

## 4.1 44 MQFP - MC81F4432Q

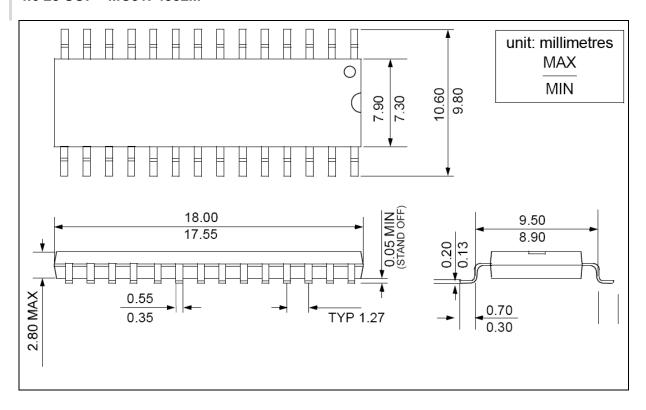

# 4.2 42 SDIP - MC81F4432K

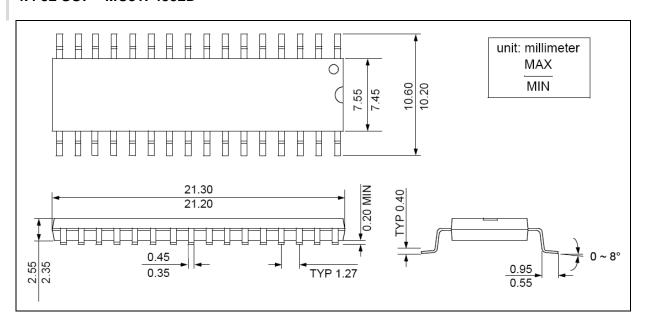

## 4.3 32 SDIP - MC81F4332K

# 4.4 32 SOP - MC81F4332D

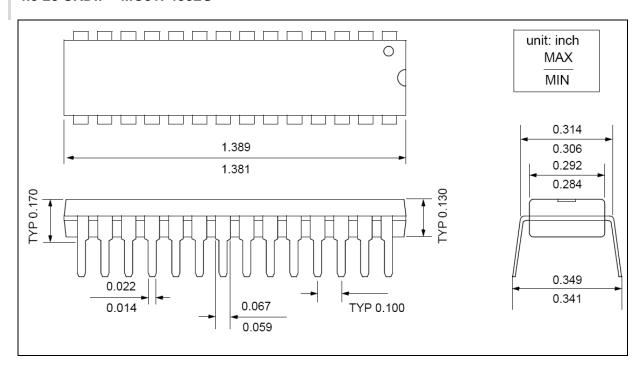

## 4.5 28 SKDIP - MC81F4332G

# 4.6 28 SOP - MC81F4332M

# **5. PIN DESCRIPTION**

| Pin Names | I/O | Function                                                                                                            | Shared with               |

|-----------|-----|---------------------------------------------------------------------------------------------------------------------|---------------------------|

| R00       |     |                                                                                                                     | SXin/EXT10                |

| R01       |     |                                                                                                                     | SXout/EXT11               |

| R02       |     |                                                                                                                     | AN0/EC0/EXT0              |

| R03       |     | This port is a 1-bit programmable I/O pin.                                                                          | AN1/T0O/<br>PWM0O/EXT1    |

| R04       | I/O | Schmitt trigger input, Push-pull, or Open-drain output port.  When used as an input port, a Pull-up resistor can be | AN2/EC1/SCK/<br>EXT2      |

| R05       |     | specified in 1-bit.                                                                                                 | AN3/SI/EXT3/<br>T1O/PWM1O |

| R06       |     |                                                                                                                     | AN4/EC2/SO/<br>EXT4       |

| R07       |     |                                                                                                                     | AN5/T2O/EXT5              |

| R10       |     |                                                                                                                     | Vref/EXT6                 |

| R11       |     |                                                                                                                     | AN6/PWM2O/<br>EXT7        |

| R12       |     | This port is a 1-bit programmable I/O pin.  Schmitt trigger input, Push-pull, or Open-drain output                  | AN7/PWM3O/<br>BUZO/EXT8   |

| R13       | I/O | port.  When used as an input port, a Pull-up resistor can be                                                        | AN8/PWM4O/<br>EXT9        |

| R14       |     | specified in 1-bit.                                                                                                 | RxD                       |

| R15       |     |                                                                                                                     | TxD                       |

| R16       | İ   |                                                                                                                     | SDA                       |

| R17       |     |                                                                                                                     | SCL                       |

| R20       |     |                                                                                                                     | AN9                       |

| R21       |     |                                                                                                                     | _                         |

| R22       |     | This port is a 1-bit programmable I/O pin.                                                                          | _                         |

| R23       | 1/0 | Input, Push-pull, or Open-drain output port.                                                                        | _                         |

| R24       | I/O | When used as an input port, a Pull-up resistor can be                                                               | _                         |

| R25       |     | specified in 1-bit.                                                                                                 | AN10                      |

| R26       |     |                                                                                                                     | AN11                      |

| R27       |     |                                                                                                                     | AN12                      |

| R30       |     |                                                                                                                     | AN13                      |

| R31       |     | This port is a 1-bit programmable I/O pin.                                                                          | AN14                      |

| R32       | I/O | Input Push-null or Open-drain output port                                                                           | _                         |

| R33       | 1/0 | When used as an input port, a Pull-up resistor can be                                                               | Xout                      |

| R34       |     | specified in 1-bit.                                                                                                 | Xin                       |

| R35       |     |                                                                                                                     | RESETB                    |

| Pin Names | I/O | Function                                              | Shared with               |

|-----------|-----|-------------------------------------------------------|---------------------------|

| R40       |     |                                                       | _                         |

| R41       |     |                                                       | _                         |

| R42       |     | This port is a 1-bit programmable I/O pin.            | ı                         |

| R43       | I/O | Input, Push-pull, or Open-drain output port.          | -                         |

| R44       | 1/0 | When used as an input port, a Pull-up resistor can be | _                         |

| R45       |     | specified in 1-bit.                                   | _                         |

| R46       |     |                                                       | _                         |

| R47       |     |                                                       | _                         |

| R50       |     | This port is a 1-bit programmable I/O pin.            | _                         |

| R51       | 1/0 | Input, Push-pull, or Open-drain output port.          | _                         |

| R52       | I/O | When used as an input port, a Pull-up resistor can be | _                         |

| R53       |     | specified in 1-bit.                                   | _                         |

| EXT0      | I/O | External interrupt input                              | R02/AN0/EC0               |

| EXT1      | I/O | External interrupt input/Timer 0 capture input        | R03/AN1/T0O/<br>PWM0O     |

| EXT2      | I/O | External interrupt input                              | R04/AN2/SCK/<br>EC1       |

| EXT3      | I/O | External interrupt input/Timer 1 capture input        | R05/AN3/SI/<br>T1O/PWM1O  |

| EXT4      | I/O | External interrupt input                              | R06/AN4/SO/<br>EC2        |

| EXT5      | I/O | External interrupt input/Timer 2 capture input        | R07/AN5/T2O               |

| EXT6      | I/O | External interrupt input/Timer 3 capture input        | R10/Vref                  |

| EXT7      |     |                                                       | R11/AN6/<br>PWM2O         |

| EXT8      |     |                                                       | R12/AN7/<br>PWM3O/BUZO    |

| EXT9      | I/O | External interrupt input                              | R13/AN8/<br>PWM4O         |

| EXT10     |     |                                                       | R00/SXin                  |

| EXT11     |     |                                                       | R01/SXout                 |

| T0O       | I/O | Timer 0 clock output                                  | R03/AN1/EXT1/<br>PWM0O    |

| PWM0O     | I/O | PWM 0 clock output                                    | R03/AN1/EXT1/<br>T0O      |

| EC0       | I/O | Timer 0 event count input                             | R02/AN0/EXT0              |

| T10       | I/O | Timer 1 clock output                                  | R05/AN3/EXT3/<br>SI/PWM1O |

| PWM1O     | I/O | PWM 1 clock output                                    | R05/AN3/EXT3/<br>SI/T1O   |

| EC1       | I/O | Timer 1 event count input                             | R04/AN2/SCK/<br>EXT2      |

| Pin Names | I/O | Function                  | Shared with                |

|-----------|-----|---------------------------|----------------------------|

| T2O       | I/O | Timer 2 clock output      | R07/AN5/EXT5               |

| EC2       | I/O | Timer 2 event count input | R06/AN4/SO/<br>EXT4        |

| PWM2O     | I/O | PWM 2 data output         | R11/AN6/EXT7               |

| PWM3O     | I/O | PWM 3 data output         | R12/AN7/EXT8/<br>BUZO      |

| PWM4O     | I/O | PWM 4 data output         | R13/AN8/EXT9               |

| BUZO      | I/O | Buzzer signal output      | R12/AN7/<br>PWM3O/EXT8     |

| AN0       |     |                           | R02/EXT0/EC0               |

| AN1       |     |                           | R03/EXT1/T0O/<br>PWM0O     |

| AN2       |     |                           | R04/EXT2/SCK<br>/EC1       |

| AN3       |     |                           | R05/EXT3/SI/<br>T1O/PWM1O  |

| AN4       |     |                           | R06/EXT4/SO/<br>EC2        |

| AN5       |     |                           | R07/EXT5/T2O               |

| AN6       | I/O | ADC input pins            | R11/EXT7/<br>PWM2O         |

| AN7       |     |                           | R12/EXT8/<br>PWM3O/BUZO    |

| AN8       |     |                           | R13/EXT9/<br>PWM4O         |

| AN9       |     |                           | R20                        |

| AN10      |     |                           | R25                        |

| AN11      |     |                           | R26                        |

| AN12      |     |                           | R27                        |

| AN13      |     |                           | R30                        |

| AN14      |     |                           | R31                        |

| RxD       | I/O | UART data input           | R14                        |

| TxD       | I/O | UART data output          | R15                        |

| SCL       | I/O | IIC-bus clock input       | R17                        |

| SDA       | I/O | IIC-bus data input/output | R16                        |

| SCK       | I/O | Serial clock input        | R04/AN2/EC1/<br>EXT2       |

| SI        | I/O | Serial data input         | R05/AN3/EXT3/<br>T1O/PWM1O |

| SO        | I/O | Serial data output        | R06/AN4/EC2/<br>EXT4       |

| Pin Names | I/O | Function                        | Shared with |

|-----------|-----|---------------------------------|-------------|

| RESETB    | I   | System reset pin                | R35         |

| XIN       | _   | Main appillator pina            | R34         |

| Xout      | _   | Main oscillator pins            | R33         |

| SXIN      |     | Cub agaillatar ning             | R00/EXT10   |

| SXout     | -   | Sub oscillator pins             | R01/EXT11   |

| VDD       | _   | Dower input pine                | _           |

| Vss       | _   | Power input pins                | _           |

| VREF      | ı   | A/D converter reference voltage | R10/EXT6    |

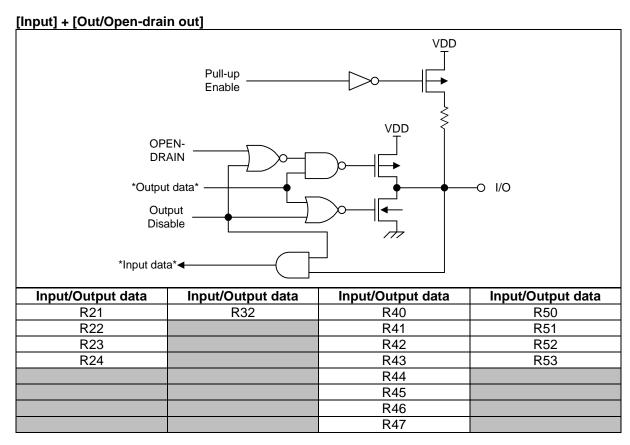

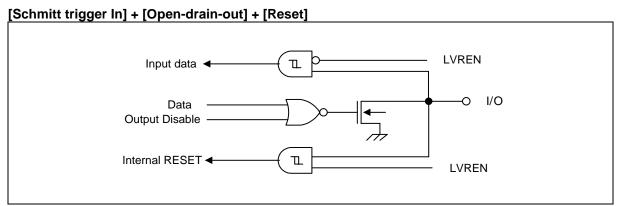

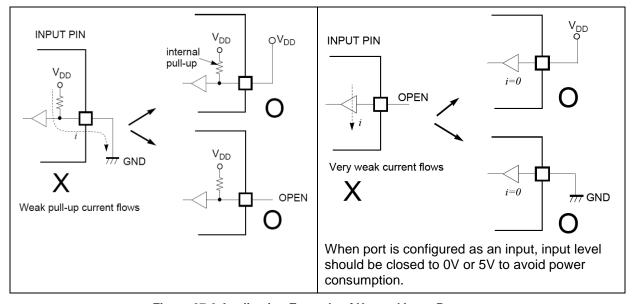

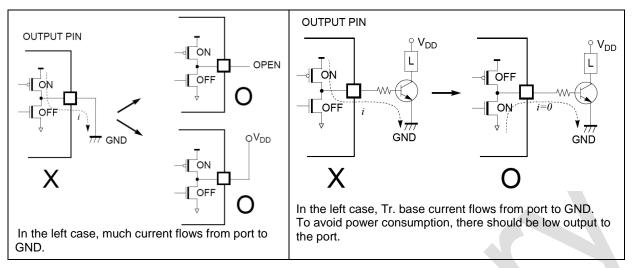

# **6. PORT STRUCTURE**

# [Schmitt trigger In] + [Out/Open-drain-out] + [Xin/Xout]

# [Schmitt trigger In] + [Out/Open-drain-out] + [SXin/SXout]

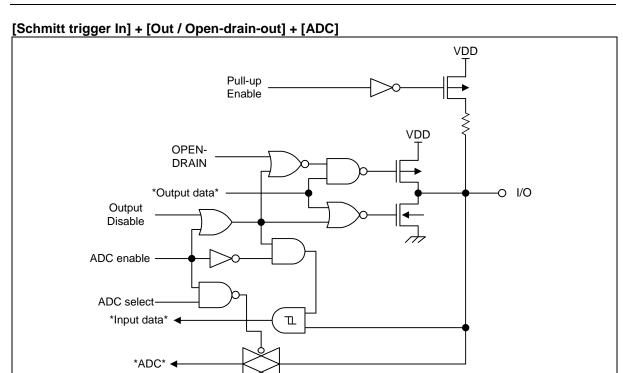

| Input/Output data | Input data   | Output data | ADC  |

|-------------------|--------------|-------------|------|

| R02               | EXT0 / EC0   | -           | AN0  |

| R03               | EXT1         | T0O/PWM0O   | AN1  |

| R04               | EXT2/SCK/EC1 | SCK         | AN2  |

| R05               | EXT3/SI      | T1O/PWM1O   | AN3  |

| R06               | EXT4/EC2     | SO          | AN4  |

| R07               | EXT5         | T2O         | AN5  |

| R10               | EXT6         | -           | Vref |

| R11               | EXT7         | PWM2O       | AN6  |

| R12               | EXT8         | PWM3O/BUZO  | AN7  |

| R13               | EXT9         | PWM4O       | AN8  |

AN13 AN14

R30

R31

R35/RESETB

## 7. ELECTRICAL CHARACTERISTICS

# 7.1 Absolute Maximum Ratings

| Parameter               | Symbol | Ratings               | Unit |

|-------------------------|--------|-----------------------|------|

| Supply Voltage          | VDD    | -0.3 <b>–</b> +6.0    | V    |

|                         | Vı     | -0.3 <b>–</b> VDD+0.3 | V    |

|                         | Vo     | -0.3 <b>–</b> VDD+0.3 | V    |

|                         | Юн     | -10                   | mA   |

| Normal Voltage Pin      | ΣІОН   | -80                   | mA   |

|                         | loL    | 60                    | mA   |

|                         | ΣΙΟL   | 120                   | mA   |

| Total Power Dissipation | fXIN   | 600                   | mW   |

| Storage Temperature     | TSTG   | -65 <b>–</b> +150     | °C   |

#### Note:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 7.2 RECOMMENDED OPERATING CONDITION

| Parameter                | Symbol          | Conditions              | Min | Тур | Max | Units |

|--------------------------|-----------------|-------------------------|-----|-----|-----|-------|

| Operating Voltage        |                 | fxin = 1.0 – 4.2MHz     | 2.2 | -   | 5.5 |       |

|                          | V <sub>DD</sub> | fxin = 1.0 - 8.0MHz     | 2.7 | -   | 5.5 | V     |

|                          |                 | fxin = 1.0 – 12.0MHz    | 4.0 | -   | 5.5 |       |

| Operating<br>Temperature | TOPR            | VDD = 2.2 <b>-</b> 5.5V | -40 |     | 85  | °C    |

# 7.3 A/D CONVERTER CHARACTERISTICS)

(T<sub>A</sub> = - 40  $^{\circ}$ C to + 85 $^{\circ}$ C, V<sub>ref</sub> = 2.7 V to 5.5 V, VSS=0V)

| Parameter                    | Symbol            | Conditions                                           | Min             | Тур  | Max  | Units |

|------------------------------|-------------------|------------------------------------------------------|-----------------|------|------|-------|

| A/D converting Resolution    | _                 | -                                                    | -               | 12   | _    | bits  |

| Integral Linearity Error     | ILE               |                                                      | _               | _    | ± 3  |       |

| Differential Linearity Error | DLE               | V ( 5 40V                                            | 1               | 1    | ± 2  |       |

| Offset Error of Top          | EOT               | Vref = 5.12V,<br>$V_{SS} = 0V, T_A = + 25 ^{\circ}C$ | _               | ±1   | ± 3  | LSB   |

| Offset Error of Bottom       | EOB               | V55 = 0V, 1A = 120 0                                 | _               | ±1   | ± 3  |       |

| Overall Accuracy             | _                 |                                                      | _               | ±3   | ±5   |       |

| Conversion time              | t <sub>CONV</sub> | -                                                    | 25              | -    | _    | μS    |

| Analog input voltage         | VAIN              | -                                                    | V <sub>SS</sub> | -    | Vref | V     |

| Analog Reference<br>Voltage  | AVref             | -                                                    | 2.7             | _    | 5.5  | V     |

| Analog input current         | I <sub>AIN</sub>  | VDD = Vref = 5V                                      | _               | _    | 10   | μА    |

|                              |                   | VDD = Vref = 5V                                      | _               | 1    | 3    | A     |

| Analog block current         | IAVDD             | VDD = Vref = 3V                                      | 1               | 0.5  | 1.5  | mA    |

| Trinaing blook darroin       | IAVDD             | VDD = Vref = 5V<br>Power down mode                   | I               | 100  | 500  | nA    |

| BGR                          | -                 | VDD = 5v, T <sub>A</sub> = + 25 °C                   | -               | 1.67 | -    | V     |

|                              | -                 | VDD = 4v, T <sub>A</sub> = + 25 °C                   | -               | 1.63 | -    | V     |

|                              | -                 | $VDD = 3v$ , $T_A = +25$ $^{\circ}C$                 | -               | 1.62 | -    | V     |

# 7.4 DC CHARACTERISTICS

(T<sub>A</sub> = - 40  $^{\circ}$ C to + 85 $^{\circ}$ C, V<sub>DD</sub> = 2.2 – 5.0V, Vss=0V, fxiN=12MHz)

| Parameter                        | Symbol                                             | Conditions                                                            | Min     | Тур     | Max     | Units |  |

|----------------------------------|----------------------------------------------------|-----------------------------------------------------------------------|---------|---------|---------|-------|--|

|                                  | VIH1                                               | R0x, R1x, R33 – R35<br>V <sub>DD</sub> = 4.5V – 5.5V                  | 0.8VDD  | _       | VDD+0.3 |       |  |

| Input High<br>Voltage            | VIH2                                               | All input pins except<br>VIH1, VIH3,<br>VDD = 4.5V – 5.5V             | 0.7VDD  | _       | VDD+0.3 | V     |  |

|                                  | VIH3                                               | Xin, Xout, SXin, SXout<br>V <sub>DD</sub> = 4.5V - 5.5V               | 0.8VDD  | -       | VDD+0.3 |       |  |

|                                  | VIL1                                               | R0x, R1x, R33 – R35<br>V <sub>DD</sub> = 4.5V – 5.5V                  | - 0.3   | _       | 0.2VDD  |       |  |

| Input Low<br>Voltage             | VIL2                                               | All input pins except<br>VIH1, VIH3,<br>V <sub>DD</sub> = 4.5V – 5.5V | - 0.3   | -       | 0.3VDD  | V     |  |

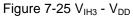

|                                  | VIL3                                               | Xin, Xout, SXin, SXout<br>$V_{DD} = 4.5V - 5.5V$                      | - 0.3   | _       | 0.2VDD  |       |  |

| Output High                      | VOH1                                               | All output ports except VOL2,<br>IOH = -2mA<br>$V_{DD} = 4.5V - 5.5V$ | VDD-1.0 | -       | -       | V     |  |

| Voltage                          | VOH2                                               | R4x, R5x<br>IOH = – 10mA<br>V <sub>DD</sub> = 4.5V – 5.5V             | VDD-2.0 | VDD-1.5 | -       | V     |  |

| Output Low                       | VOL1                                               | All output ports except VOL2, IOL=15mA VDD = 4.5V - 5.5V              | -       | _       | 2.0     | >     |  |

| Voltage                          | VOL2                                               | R4x, R5x<br>IOL=60mA<br>V <sub>DD</sub> = 4.5V – 5.5V                 | -       | 1.5     | 2.0     | V     |  |

| Input high<br>leakage<br>current | IIH                                                | R0x – R5x, Vin=VDD                                                    | -       | -       | 1       | uA    |  |

| Input low leakage current        | IIL                                                | R0x – R5x, Vin=Vss                                                    | - 1     | -       | -       | uA    |  |

|                                  | VI=0V, TA=25 °C,<br>R0x – R5x except R35<br>VDD=5V |                                                                       | 25      | 50      | 100     | 2     |  |

| Pull-up resistor                 | RPU                                                | VI=0V, TA=25 °C,<br>R0x – R5x except R35<br>VDD=3V                    | 50      | 100     | 200     | kΩ    |  |

# 7.5 DC CHARACTERISTICS(continued)

$(T_A = -40 \, ^{\circ}\text{C to} + 85 \, ^{\circ}\text{C}, \, V_{DD} = 2.2 - 5.0\text{V}, \, \text{Vss=0V}, \, \text{fxin=12MHz})$

| Parameter          | Symbol  | Conditions                                                               | Min  | Тур   | Max   | Units |

|--------------------|---------|--------------------------------------------------------------------------|------|-------|-------|-------|

| OSC feedback       | RX1     | Xin=VDD, Xout=VSS<br>TA=25 °C, VDD=5V                                    | 350  | 700   | 1500  | ΜΩ    |

| resistor           | RX2     | SXin=VDD, SXout=VSS<br>TA=25 °C, VDD=5V                                  | 1800 | 3600  | 5400  | IVIC2 |

|                    | IDD1    | Active mode,<br>fx=12MHz, VDD=5V±10%<br>Crystal oscillator               | -    | 8.0   | 15.0  | mA    |

|                    |         | fx=8MHz, VDD=3V±10%                                                      | _    | 3.0   | 6.0   |       |

|                    | ISLEEP1 | Sleep mode, fx=12MHz, VDD=5V±10% Crystal oscillator                      |      | 2.0   | 4.0   | mA    |

| Complete accompany |         | fx=8MHz, VDD=3V±10%                                                      | _    | 1.0   | 2.0   |       |

| Supply current     | IDD2    | Active mode,<br>fx=32.768kHz, VDD=3V±10%<br>Crystal oscillator, TA=25 °C | -    | 150.0 | 300.0 | uA    |

|                    | ISLEEP2 | Sleep mode,<br>fx=32.768kHz, VDD=3V±10%<br>Crystal oscillator, TA=25 °C  | -    | 6.0   | 12.0  | uA    |

|                    | ISTOP   | Stop mode<br>VDD=5.5V, TA=25 °C                                          | -    | 0.5   | 5.0   | uA    |

| POR level          |         |                                                                          | 1.82 |       | 2.1   | V     |

# 7.6 Input/output Capacitance

$(T_A = -40 \, ^{\circ}C \text{ to } + 85 \, ^{\circ}C, \, V_{DD} = 0 \, \text{V})$

| Parameter          | Symbol | Conditions                        | Min | Тур | Max | Units |

|--------------------|--------|-----------------------------------|-----|-----|-----|-------|

| Input Capacitance  | CIN    | f=1MHz                            |     |     |     |       |

| Output Capacitance | COUT   | Unmeasured pins are connected Vss | _   | _   | 10  | pF    |

| I/O Capacitance    | CIO    |                                   |     |     |     |       |

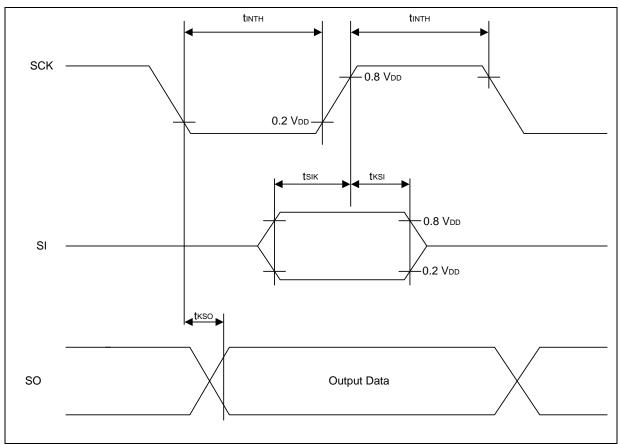

# 7.7 Serial I/O Characteristics

$(T_A = -40 \, ^{\circ}\text{C to} + 85 \, ^{\circ}\text{C}, \, V_{DD} = 2.2 \, \text{V to} \, 5.5 \, \text{V})$

| Parameter                        | Symbol                                   | Conditions                           | Min                    | Тур | Max | Units |

|----------------------------------|------------------------------------------|--------------------------------------|------------------------|-----|-----|-------|

| SCK cycle time                   | turni                                    | External SCK source                  | 1,000                  |     |     | nS    |

| SCK Cycle time                   | t <sub>KCY</sub>                         | Internal SCK source                  | 1,000                  |     |     | 29    |

| 001411111111111                  |                                          | External SCK source                  | 500                    |     |     | 9     |

| SCK high, low width              | t <sub>KH</sub> , t <sub>KL</sub>        | Internal SCK source                  | t <sub>KCY</sub> /2–50 |     |     | nS    |

| SI setup time                    | t                                        | External SCK source                  | 250                    |     | _   | 5     |

| to SCK high                      | t <sub>SIK</sub>                         | Internal SCK source                  | 250                    |     |     | nS    |

| SI hold time to SCK              | t                                        | External SCK source                  | 400                    |     |     | nS    |

| High                             | <sup>t</sup> KSI                         | Internal SCK source                  | 400                    |     |     | 2     |

| Output delay for                 | t                                        | External SCK source                  |                        |     | 300 | 5     |

| SCK to SOUT                      | t <sub>KSO</sub>                         | Internal SCK source                  | _                      | _   | 250 | nS    |

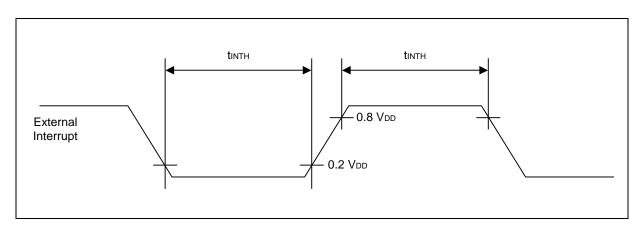

| Interrupt input, high, low width | t <sub>INTH</sub> ,<br>t <sub>INTL</sub> | All interrupt, V <sub>DD</sub> = 5 V | 200                    | _   | _   | nS    |

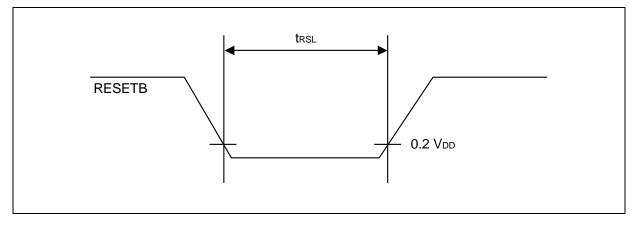

| RESETB input low width           | t <sub>RSL</sub>                         | Input, V <sub>DD</sub> = 5 V         | 10                     | _   | _   | uS    |

**Figure 7-1 Input Timing for External Interrupts**

# Figure 7-2 Input Timing for RESETB

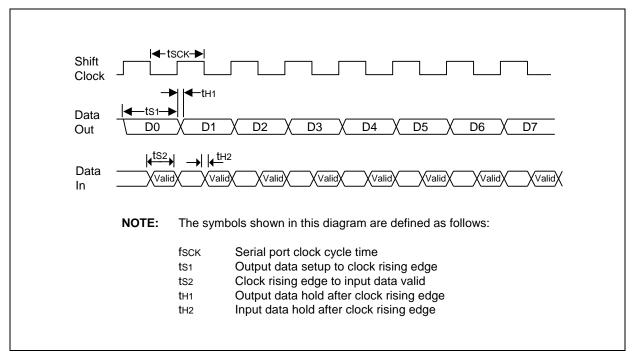

Figure 7-3 Serial Interface Data Transfer Timing

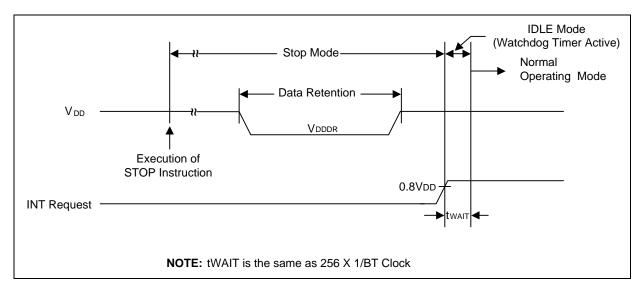

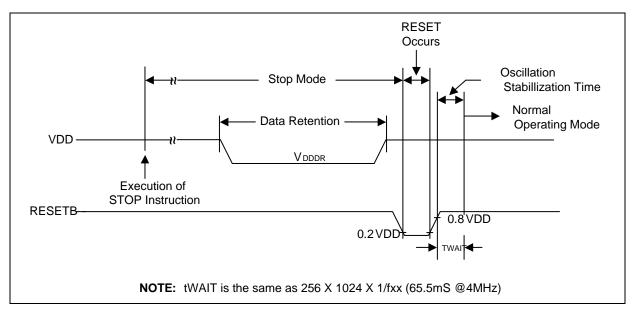

# 7.8 Data Retention Voltage in Stop Mode

$$(T_A = -40 \, ^{\circ}C \text{ to} + 85 \, ^{\circ}C, \, V_{DD} = 2.2 \, \text{V to} \, 5.5 \, \text{V})$$

| Parameter                     | Symbol | Conditions                                            | Min | Тур | Max | Units |

|-------------------------------|--------|-------------------------------------------------------|-----|-----|-----|-------|

| Data retention supply voltage | VDDDR  | -                                                     | 2.2 | -   | 5.5 | V     |

| Data retention supply current | IDDDR  | $V_{DDDR} = 2.2V$ (T <sub>A</sub> = 25 °C), Stop mode | _   | _   | 1   | uA    |

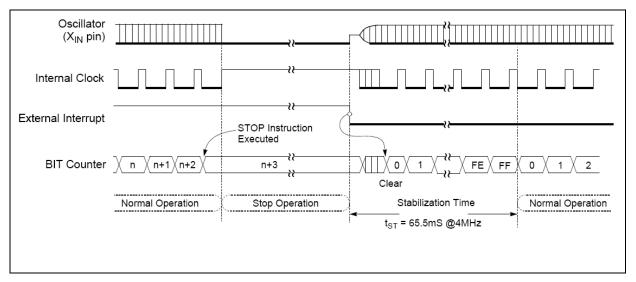

Figure 7-4 Stop Mode Release Timing When Initiated by an Interrupt

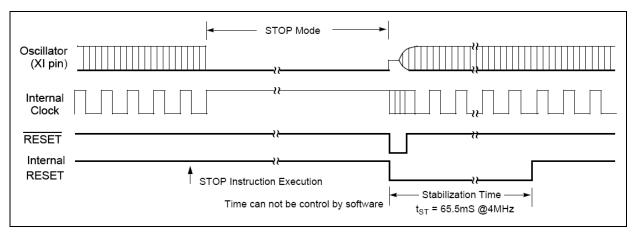

Figure 7-5 Stop Mode Release Timing When Initiated by RESETB

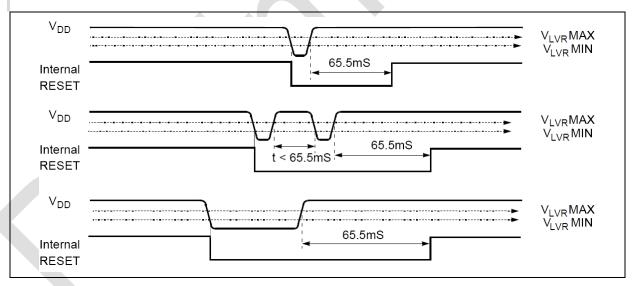

# 7.9 LVR (Low Voltage Reset) Electrical Characteristics

$$(T_A = -40 \, ^{\circ}\text{C to} + 85 \, ^{\circ}\text{C}, \, V_{DD} = 2.2 \, \text{V to} \, 5.5 \, \text{V})$$

| Parameter                 | Symbol | Conditions | Min | Тур | Max | Units |

|---------------------------|--------|------------|-----|-----|-----|-------|

|                           |        |            | 2.2 | 2.4 | 2.6 |       |

| LVD voltogo               | VLVR   | LVR –      | 2.5 | 2.7 | 2.9 | V     |

| LVR voltage               |        |            | 2.7 | 3.0 | 3.3 | V     |

|                           |        |            | 3.6 | 4.0 | 4.4 |       |

| Hysteresis voltage of LVR | △V     | _          | _   | 10  | 100 | mV    |

| Current consumption       | ILVR   | VDD = 3V   | ı   | 45  | 80  | uA    |

#### Note:

- 1. The current of LVR circuit is consumed when LVR is enabled by "ROM Option".

- 2.  $2^{16}/fx$  ( = 6.55 ms at fx = 10 MHz)

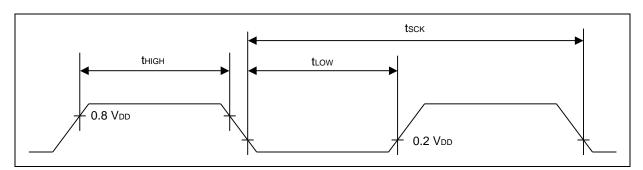

# 7.10 UART Timing Characteristics

$$(T_A = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}, \, V_{DD} = 2.2 \,\text{V} \, \text{to} \, 5.5 \,\text{V})$$

| Parameter                                | Symbol                               | Min                   | Тур                   | Max  | Units |

|------------------------------------------|--------------------------------------|-----------------------|-----------------------|------|-------|

| Serial port clock cycle time             | t <sub>SCK</sub>                     | 1250                  | t <sub>CPU</sub> × 16 | 1650 |       |

| Output data setup to clock rising edge   | t <sub>S1</sub>                      | 590                   | t <sub>CPU</sub> × 13 | _    |       |

| Clock rising edge to input data valid    | t <sub>S2</sub>                      | _                     | _                     | 590  |       |

| Output data hold after clock rising edge | t <sub>H1</sub>                      | t <sub>CPU</sub> – 50 | t <sub>CPU</sub>      | -    | nS    |

| Input data hold after clock rising edge  | t <sub>H2</sub>                      | 0                     | _                     | _    |       |

| Serial port clock High, Low level width  | t <sub>HIGH</sub> , t <sub>LOW</sub> | 470                   | t <sub>CPU</sub> × 8  | 970  |       |

Figure 7-6 Waveform for UART Timing Characteristics

Figure 7-7 Timing Waveform for the UART Module

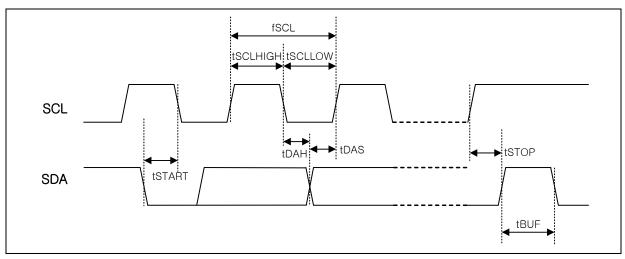

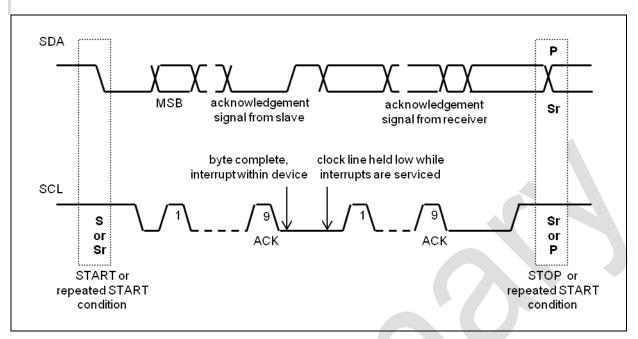

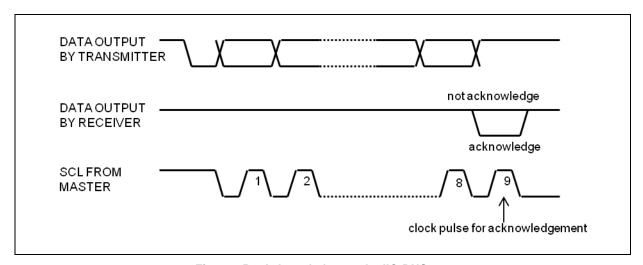

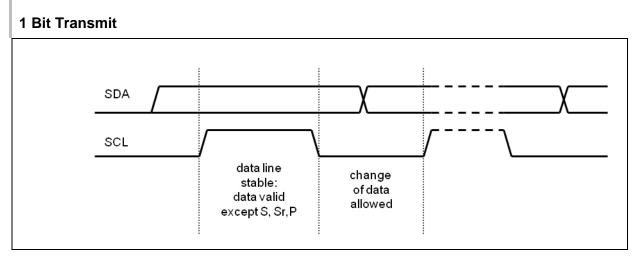

# 7.11 IIC Timing Characteristics

$$(T_A = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}, \, V_{DD} = 2.2 \,\text{V to} \, 5.5 \,\text{V})$$

| Parameter                  | Condition             | Symbol               | Min  | Тур. | Max                    | Units |

|----------------------------|-----------------------|----------------------|------|------|------------------------|-------|

| SCL clock frequency        | ı                     | t <sub>SCL</sub>     | I    | ı    | 100(std.)<br>400(fast) | kHz   |

| SCL high level pulse width |                       | t <sub>SCLHIGH</sub> | 4.0  | -    | -                      | us    |

| SCL low level pulse width  |                       | t <sub>SCLLOW</sub>  | 4.7  | I    | ı                      | us    |

| BUS free time              |                       | t <sub>BUF</sub>     | 4.7  | ı    | _                      | us    |

| Start hold time            | SCL clock<br>= 100kHz | t <sub>START</sub>   | 4.0  | ı    | -                      | us    |

| Stop setup time            |                       | t <sub>STOP</sub>    | 4.0  | ı    | -                      | us    |

| Data hold time             |                       | t <sub>DAH</sub>     | 0    | ı    | _                      | us    |

| Data setup time            |                       | t <sub>DAS</sub>     | 0.25 | _    | _                      | us    |

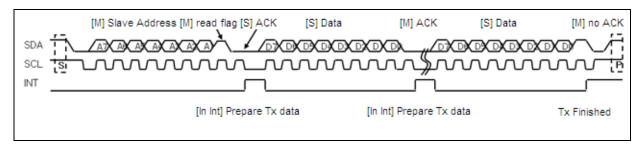

Figure 7-8 Waveform for IIC Timing Characteristics

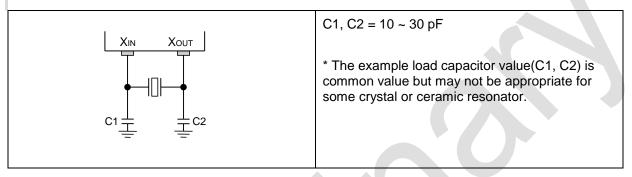

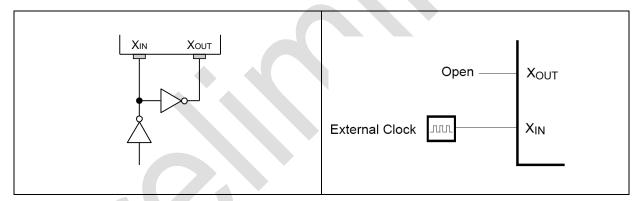

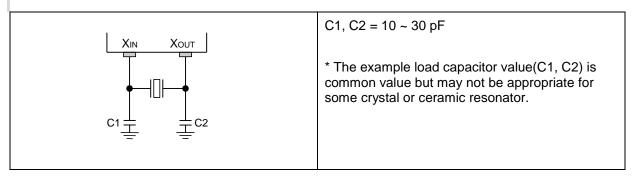

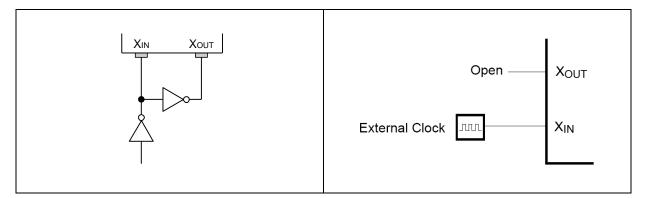

### 7.12 Main clock Oscillator Characteristics

$(T_A = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}, \, V_{DD} = 2.2 \,\text{V to} \, 5.5 \,\text{V})$

| Oscillator            | Parameter                       | Conditions    | Min | Тур. | Max  | Units |

|-----------------------|---------------------------------|---------------|-----|------|------|-------|

|                       |                                 | 2.2 V – 5.5 V | 1.0 | _    | 4.2  |       |

| Crystal               | Main oscillation frequency      | 2.7 V – 5.5 V | 1.0 | _    | 8.0  | MHz   |

|                       |                                 | 4.0 V – 5.5 V | 1.0 | _    | 12.0 |       |

|                       | Main oscillation frequency      | 2.2 V – 5.5 V | 1.0 | _    | 4.2  |       |

| Ceramic<br>Oscillator |                                 | 2.7 V – 5.5 V | 1.0 | _    | 8.0  | MHz   |

|                       |                                 | 4.0 V – 5.5 V | 1.0 | _    | 12.0 |       |

|                       |                                 | 2.2 V – 5.5 V | 1.0 | _    | 4.2  |       |

| External<br>Clock     | X <sub>IN</sub> input frequency | 2.7 V – 5.5 V | 1.0 | _    | 8.0  | MHz   |

|                       |                                 | 4.0 V – 5.5 V | 1.0 | _    | 12.0 |       |

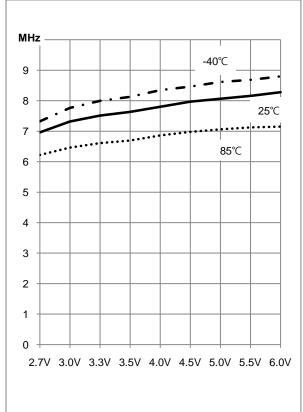

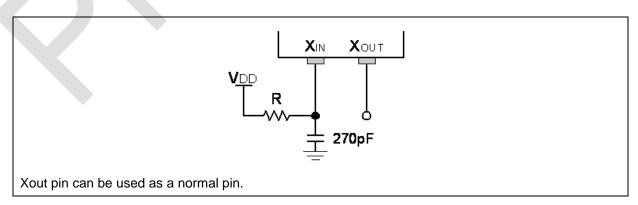

### 7.13 External RC Oscillation Characteristics

$(T_A = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}, \, V_{DD} = 2.2 \,\text{V to} \, 5.5 \,\text{V})$

| Parameter                                       | Symbol | Conditions                                                                   | Min  | Тур. | Max  | Units |

|-------------------------------------------------|--------|------------------------------------------------------------------------------|------|------|------|-------|

| RC oscillator frequency<br>Range <sup>(1)</sup> | fERC   | T <sub>A</sub> = 25°C                                                        | 1    | _    | 8    | MHz   |

| Assume of DC                                    |        | V <sub>DD</sub> =5.5V, T <sub>A</sub> = 25°C                                 | - 6  | _    | + 6  |       |

| Accuracy of RC Oscillation (2)                  | ACCERC | $V_{DD} = 5.5V$ ,<br>$T_{A} = -40 ^{\circ}\text{C to} + 85 ^{\circ}\text{C}$ | - 12 | -    | + 12 | %     |

| RC oscillator setup time (3)                    | tSUERC | $T_A = 25^{\circ}C$                                                          | _    | _    | 10   | mS    |

#### Note

- 1. The external resistor is connected between  $V_{DD}$  and  $X_{IN}$  pin and the 270pF capacitor is connected between  $X_{IN}$  and  $V_{SS}$  pin. ( $X_{OUT}$  pin can be used as a normal port). The frequency is adjusted by external resistor.

- 2. The min/max frequencies are within the range of RC OSC frequency (1MHz to 8MHz)

- 3. Data based on characterization results, not tested in production

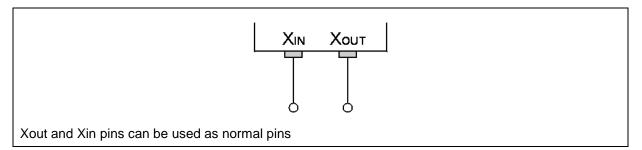

### 7.14 Internal RC Oscillation Characteristics

$(T_A = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}, \, V_{DD} = 2.2 \,\,\text{V to} \,\, 5.5 \,\,\text{V})$

| Parameter                    | Symbol | Conditions                                                            | Min  | Тур. | Max | Units |

|------------------------------|--------|-----------------------------------------------------------------------|------|------|-----|-------|

|                              |        | V <sub>DD</sub> =5.5V, T <sub>A</sub> = 25°C                          | -4%  | 8.0  | 4%  |       |

| RC oscillator frequency (1)  | fIRC   | $V_{DD} = 5.5V$ ,<br>$T_{A} = -40^{\circ}C \text{ to } + 85^{\circ}C$ | -20% | 8.0  | 20% | MHz   |

| Clock duty ratio             | TOD    | -                                                                     | 40   | 50   | 60  | %     |

| RC oscillator setup time (2) | tSUIRC | $T_A = 25^{\circ}C$                                                   | _    | _    | 10  | mS    |

Note:

1. Data based on characterization results, not tested in production

2.  $X_{\mbox{IN}}$  and  $X_{\mbox{OUT}}$  pins can be used as I/O ports.

# 7.15 Sub clock Oscillator Characteristics

$(T_A = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}, \, V_{DD} = 2.2 \,\text{V to} \, 5.5 \,\text{V})$

| Oscillator     | Parameter                        | Conditions    | Min | Тур.   | Max | Units |

|----------------|----------------------------------|---------------|-----|--------|-----|-------|

| Crystal        | Sub oscillation frequency        | 2.2 V – 5.5 V | 32  | 32.768 | 35  | KHz   |

| External Clock | SX <sub>IN</sub> input frequency | 2.2 V – 5.5 V | 32  | -      | 100 | KHz   |

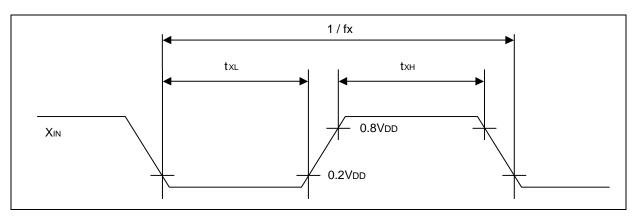

# 7.16 Main Oscillation Stabilization Time

$(T_A = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}, \, V_{DD} = 2.2 \,\text{V to} \, 5.5 \,\text{V})$

| Oscillator     | Conditions                                                                                              | Min  | Тур. | Max | Units |

|----------------|---------------------------------------------------------------------------------------------------------|------|------|-----|-------|

| Crystal        | fx > 1 MHz                                                                                              | _    | _    | 60  | mS    |

| Ceramic        | Oscillation stabilization occurs when V <sub>DD</sub> is equal to the minimum oscillator voltage range. | -    | -    | 10  | mS    |

| External Clock | $X_{IN}$ input high and low width $(t_{XH}, t_{XL})$                                                    | 40.0 | _    | 480 | nS    |

Figure 7-9 Clock Timing Measurement at XIN

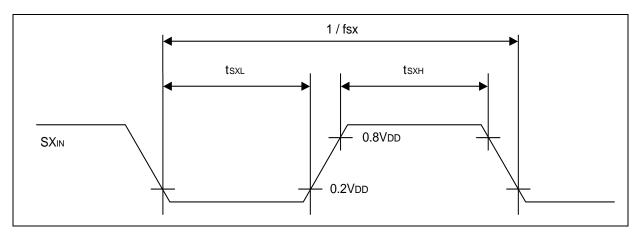

# 7.17 Sub Oscillation Stabilization Time

$$(T_A = -40 \,^{\circ}\text{C to} + 85 \,^{\circ}\text{C}, \, V_{DD} = 2.2 \,\,\text{V to} \,\, 5.5 \,\,\text{V})$$

| Oscillator     | Conditions                                            | Min | Тур. | Max | Units |

|----------------|-------------------------------------------------------|-----|------|-----|-------|

| Crystal        | _                                                     | _   | _    | 10  | S     |

| External Clock | $SX_{IN}$ input high and low width $(t_{XH}, t_{XL})$ | 5   | -    | 15  | uS    |

Figure 7-10 Clock Timing Measurement at SXIN

# 7.18 Operating Voltage Range

Figure 7-11 Operating Voltage Range

# 7.19 Typical Characteristics

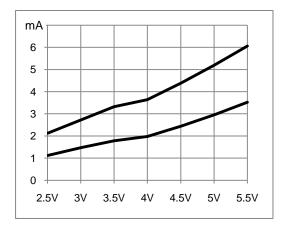

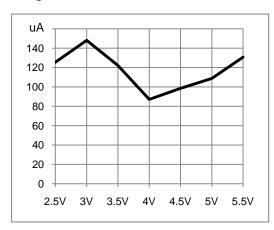

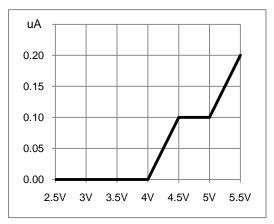

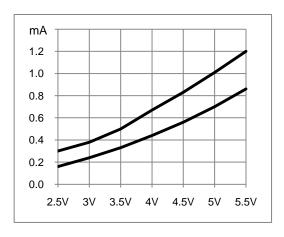

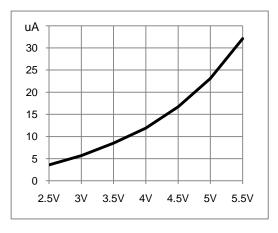

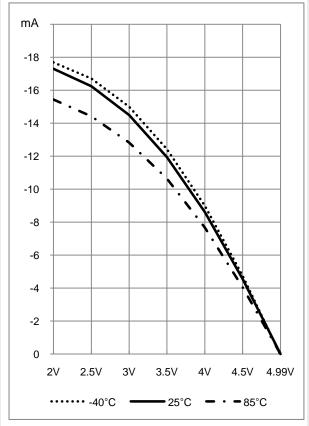

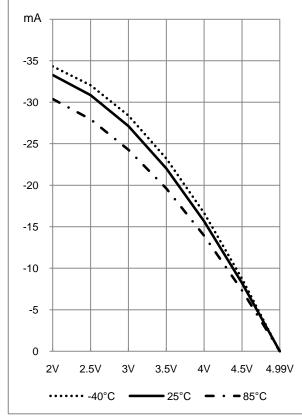

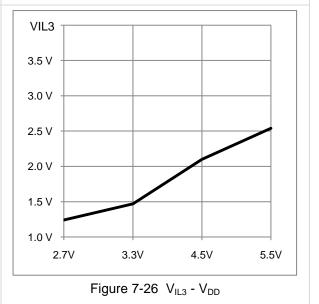

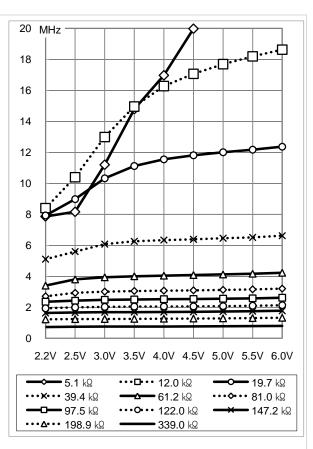

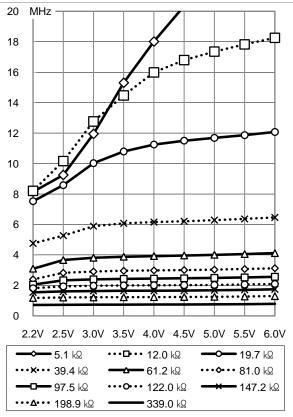

These graphs and tables provided in this section are for design guidance only and are not tested or guaranteed. In some graphs or tables the data presented are outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are guaranteed to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

Figure 7-12 I<sub>DD</sub> - V<sub>DD</sub> in Normal Mode

Figure 7-14 I<sub>DD2</sub> - V<sub>DD</sub> in Sub Active Mode

Figure 7-16  $I_{STOP}$  –  $V_{DD}$  in STOP Mode

Figure 7-13 I<sub>SLEEP</sub> - V<sub>DD</sub> in Sleep Mode

Figure 7-15 I<sub>SLEEP2</sub> - V<sub>DD</sub> with Sub Clock

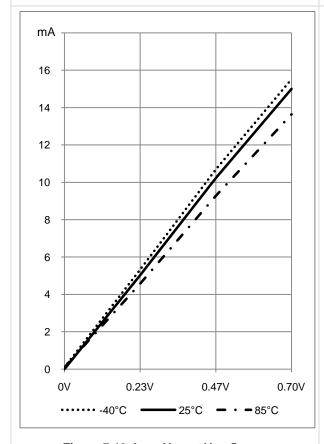

Figure 7-17 I<sub>OH1</sub> - V<sub>OH1</sub> at V<sub>DD</sub>=5v

Figure 7-18 I<sub>OH2</sub> - V<sub>OH2</sub> at V<sub>DD</sub>=5V

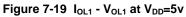

Figure 7-20  $I_{OL2}$  -  $V_{OL2}$  at  $V_{DD}$ =5v

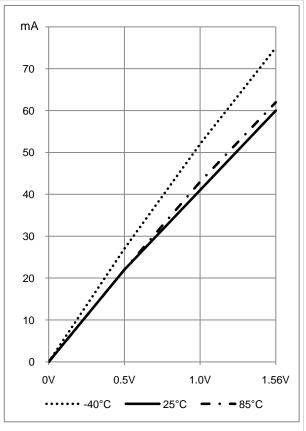

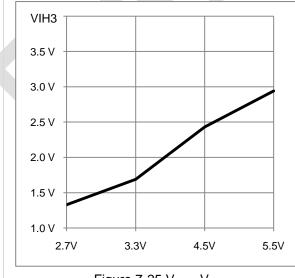

Figure 7-21 V<sub>IH1</sub> - V<sub>DD</sub>

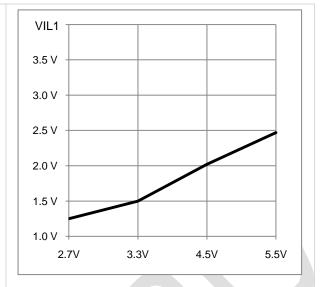

Figure 7-22 V<sub>IL1</sub> - V<sub>DD</sub>

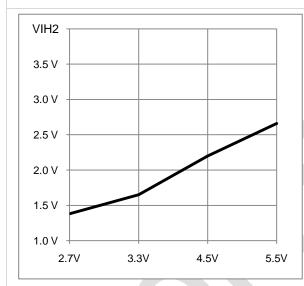

Figure 7-23 V<sub>IH2</sub> - V<sub>DD</sub>

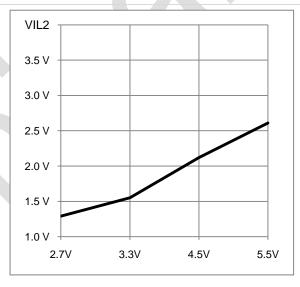

Figure 7-24 V<sub>IL2</sub> - V<sub>DD</sub>

Figure 7-27 8MHz Internal OSC Freq. - VDD

Figure 7-29 Ext. R/C OSC Freq. - V<sub>DD</sub> at 85°C

Figure 7-28 Ext. R/C OSC Freq. - V<sub>DD</sub> at 25°C

Figure 7-30 Ext.I R/C OSC Freq. - V<sub>DD</sub> at -40°C

### 8. ROM OPTION

The ROM Option is a start-condition byte of the chip. The default ROM Option value is 00H (LVR enable and External RC is selected). It can be changed by appropriate writing tools such as PGMPlusUSB, ISP, etc.

# 8.1 Rom Option

|        | 7     | 6  | 5  | 4 | 3 | 2 | 1    | 0 |

|--------|-------|----|----|---|---|---|------|---|

| ROM    | LVREN | LV | RS | _ | _ |   | OSCS |   |

| OPTION |       |    |    |   |   |   |      |   |

| LVREN | LVR Enable/Disable bit        | 0: Enable (R35)                 |  |  |  |

|-------|-------------------------------|---------------------------------|--|--|--|

| LVKEN | LVK Enable/Disable bit        | 1: Disable (RESETB)             |  |  |  |

|       |                               | 00: 2.4V                        |  |  |  |

| LVDS  | LVRS LVR Level Selection bits | 01: 2.7V                        |  |  |  |

| LVKS  |                               | 10: 3.0V                        |  |  |  |

|       |                               | 11: 4.0V                        |  |  |  |

| _     | bit4 – bit3                   | Not used in MC81F4x32           |  |  |  |

|       |                               | 000: External RC                |  |  |  |

|       |                               | 001: Internal RC; 4MHz          |  |  |  |

|       |                               | 010: Internal RC; 2MHz          |  |  |  |

| 0000  | Ossillator Salastian hita     | 011: Internal RC; 1MHz          |  |  |  |

| oscs  | Oscillator Selection bits     | 100: Internal RC; 8MHz          |  |  |  |

|       |                               | 101: Not available ( Note 4 )   |  |  |  |

|       |                               | 110: Not available ( Note 5 )   |  |  |  |

|       |                               | 111: Crystal/ceramic oscillator |  |  |  |

#### Note:

- 1. When LVR is enabled, LVR level should be set to appropriate value, not default value.

- 2. When you select the Crystal/ceramic oscillator, R33 and R34 pins are automatically selected for XIN and XOUT mode.

- 3. When you select the external RC, R34 pin is automatically selected for XIN mode.

- 4. If OSCS is set by '101', Oscillator works as 'Internal RC; 4MHz' mode.

- 5. If OSCS is set by '110', Oscillator works as 'Internal RC; 2MHz' mode.

# 8.2 Read Timing

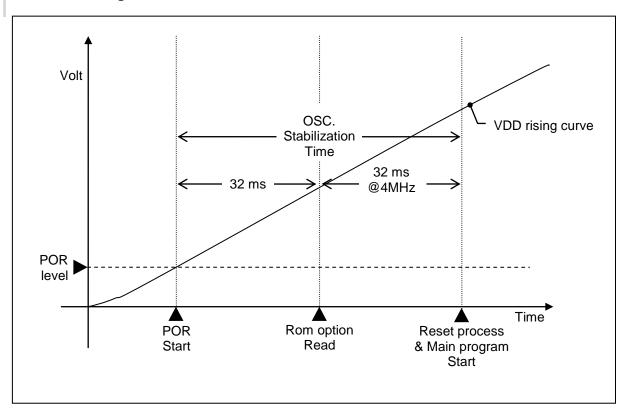

Figure 8-1 ROM option read timing diagram

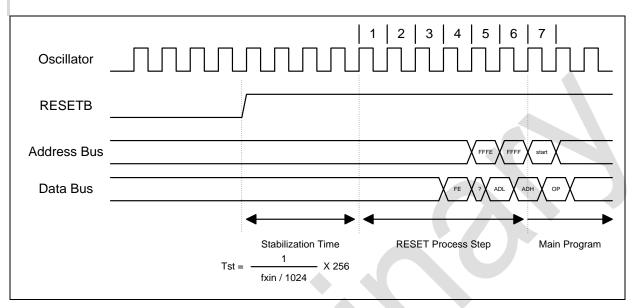

Rom option is affected 32 mili-second (typically) after VDD cross the POR level. More precisely saying, the 32 mili-second is the time for 1/2 counting of 1024 divided BIT with 4 MHz internal OSC. After the ROM option is affected, system clock source is changed based on the ROM option. And then, rest 1/2 counting is continued with changed clock source. So, hole stabilization time is variable depend on the clock source.

|              | Before read<br>ROM option            | After read<br>ROM option              | OSC Stabilization Time |

|--------------|--------------------------------------|---------------------------------------|------------------------|

| Formula      | 250ns x 128(BTCR) x<br>1024(divider) | Period x 128(BTCR) x<br>1024(divider) | Before + After         |

| Int-RC 4MHz  | 32 ms                                | 32 ms                                 | 64 ms                  |

| Int-RC 8MHz  | 32 ms                                | 16 ms                                 | 48 ms                  |

| X-tal 12 MHz | 32 ms                                | 10.7 ms                               | 42.7 ms                |

| X-tal 16 Mhz | 32 ms                                | 8 ms                                  | 40 ms                  |

Table 8-1 examples of OSC stabilization time

Note that ROM option is affected in OSC stabilization time. So even you change the ROM option by ISP. It is not affected until system is reset. In other words, you must reset the system after change the ROM option.

#### 9. MEMORY ORGANIZATION

This MCU has separated address spaces for the \*program memory\* and the \*data Memory\*.

The program memory is a ROM which stores a program code. It is not possible to write a data at the program memory while the MCU is running.

The Data Memory is a REM which is used by MCU at running time.

### 9.1 Registers

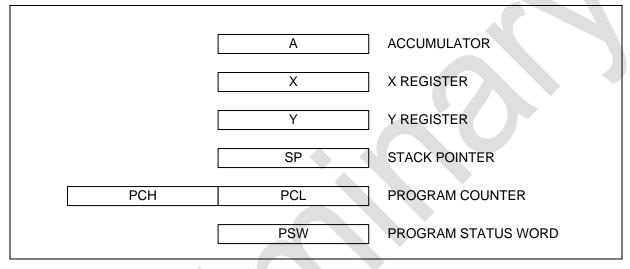

There are few registers which are used for MCU operating.

Figure 9-1 Configuration of Registers

**Accumulator( A Register )**: Accumulator is the 8-bit general purpose register, which is used for accumulating and some data operations such as transfer, temporary saving, and conditional judgment, etc.

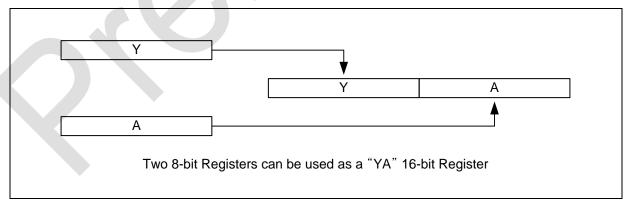

And it can be used as a part of 16-bit register with Y Register as shown below.

Figure 9-2 Configuration of YA 16-bit Registers

**X, Y Registers**: In the addressing mode, these are used as a index register. It makes it possible to access at Xth or Yth memory from specific address. It is extremely effective for referencing a subroutine table and a memory table.

These registers also have increment, decrement, comparison and data transfer functions, and they can be used as a simple accumulator.

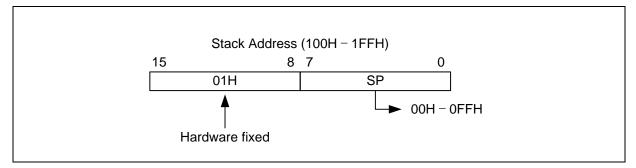

Figure 9-3 Stack Pointer

**Stack Pointer**: Stack Pointer is an 8-bit register which indicates the current 'push' point in the stack area. It is used to push and pop when interrupts or general function call is occurred. Stack Pointer identifies the location in the stack to be accessed (save or restore).

Generally, SP is automatically updated when a subroutine call is executed or an interrupt is accepted. However, if it is used in excess of the stack area permitted by the data memory allocating configuration, the user-processed data may be lost.

The stack can be located at any position within 100H to 1FFH of the internal data memory. The SP is not initialized by hardware, requiring to write the initial value (the location with which the use of the stack starts) by using the initialization routine. Normally, the initial value of "FFH" is used.

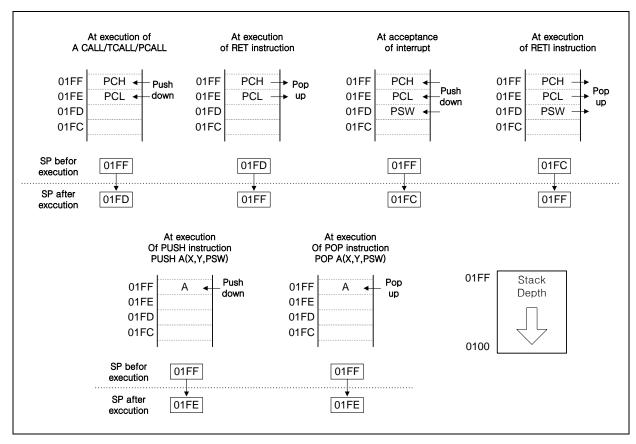

Figure 9-4 Stack Operation

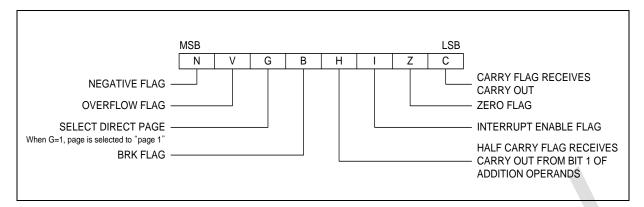

Figure 9-5 PSW ( Program Status Word ) Registers

**Program Status Word**: Program Status Word (PSW)contains several bits that reflect the current state of the CPU. It contains the Negative flag, the Overflow flag, the Break flag the Half Carry (for BCD operation), the Interrupt enable flag, the Zero flag, and the Carry flag.

### [Carry flag C]

This flag stores any carry or borrow from the ALU of CPU after an arithmetic operation and is also changed by the Shift Instruction or Rotate Instruction.

#### [Zero flag Z]

This flag is set when the result of an arithmetic operation or data transfer is "0" and is cleared by any other result.

#### [Interrupt disable flag I]

This flag enables/disables all interrupts except interrupt caused by Reset or software BRK instruction. All interrupts are disabled when cleared to "0". This flag immediately becomes "0" when an interrupt is served. It is set by the EI instruction and cleared by the DI instruction.

#### [Half carry flag H]

After operation, this is set when there is a carry from bit 3 of ALU or there is no borrow from bit 4 of ALU. This bit can not be set or cleared except CLRV instruction with Overflow flag (V).

# [Break flag B]

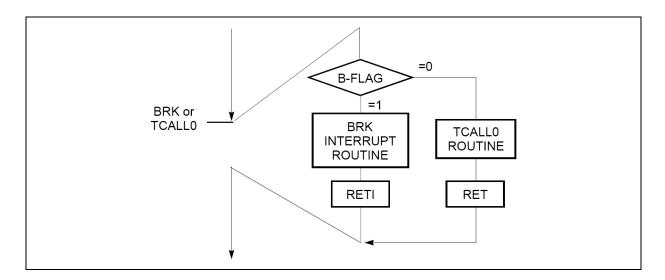

This flag is set by software BRK instruction to distinguish BRK from TCALL instruction with the same vector address.

#### [Direct page flag G]

This flag assigns RAM page for direct addressing mode. In the direct addressing mode, addressing area is from zero page 00H to 0FFH when this flag is "0". If it is set to "1", addressing area is assigned 100H to 1FFH. It is set by SETG instruction and cleared by CLRG.

#### [Overflow flag V]

This flag is set to "1" when an overflow occurs as the result of an arithmetic operation involving signs. An overflow occurs when the result of an addition or subtraction exceeds +127(7FH) or -128(80H). The CLRV instruction clears the overflow flag. There is no set instruction. When the BIT instruction is executed, bit 6 of memory is copied to this flag.

#### [Negative flag N]

This flag is set to match the sign bit (bit 7) status of the result of a data or arithmetic operation. When the BIT instruction is executed, bit 7 of memory is copied to this flag.

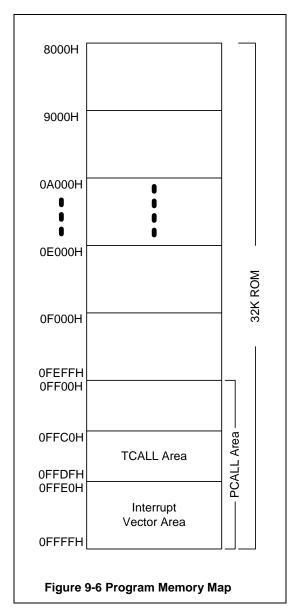

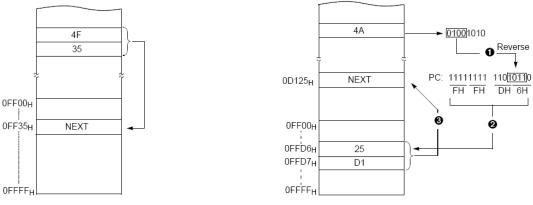

### 9.2 Program Memory

A 16-bit program counter is capable of addressing up to 64K bytes, but this device has 32K bytes program memory space only physically implemented. Accessing a location above FFFFH will cause a wrap-around to 0000H.

Figure 9-6 shows a map of Program Memory. After reset, the CPU begins execution from reset vector which is stored in address FFFEH and FFFFH. As shown in Figure 9-6, each area is assigned a fixed location in Program Memory.

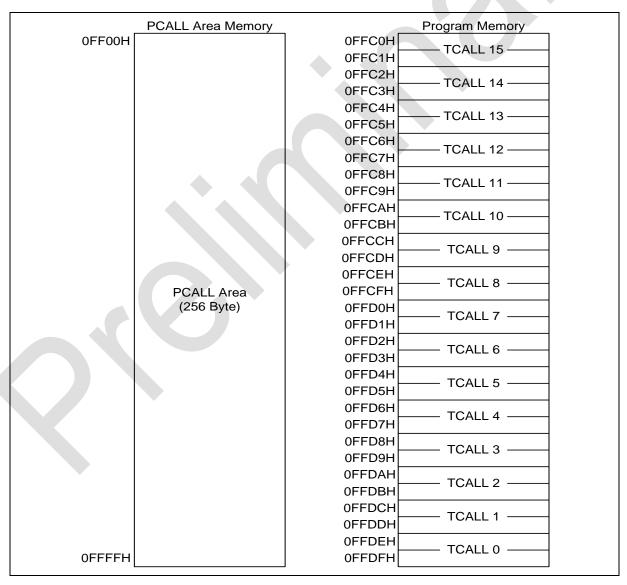

Program memory area contains the user program Page Call (PCALL) area contains subroutine program to reduce program byte length by using 2 bytes PCALL instead of 3 bytes CALL instruction. If it is frequently called, it is more useful to save program byte length.

Table Call (TCALL) causes the CPU to jump to each TCALL address, where it commences the execution of the service routine. The Table Call service area spaces 2-byte for every TCALL: 0FFC0H for TCALL15, 0FFC2H for TCALL14, etc., as shown in Figure 9-7.

The interrupt causes the CPU to jump to specific location where it commences the execution of the service routine. The interrupt service locations spaces 2-byte interval. The External interrupt 1, for Example, is assigned to location 0FFFCH.

Any area from 0FF00H to 0FFFFH, if it is not going to be used, its service location is available as general purpose Program Memory.

Figure 9-7 PCALL and TCALL Memory Area

# **Example:** Usage of TCALL

```

LDA #5

TCALL 0FH ;1BYTE INSTRUCTION

: ;INSTEAD OF 3 BYTES

: ;NORMAL CALL

;TABLE CALL ROUTINE

FUNC_A: LDA LRG0

RET

FUNC_B: LDA LRG1

RET

;TABLE CALL ADD. AREA

ORG 0FFC0H ;TCALL ADDRESS AREA

DW FUNC_A

DW FUNC_B

```

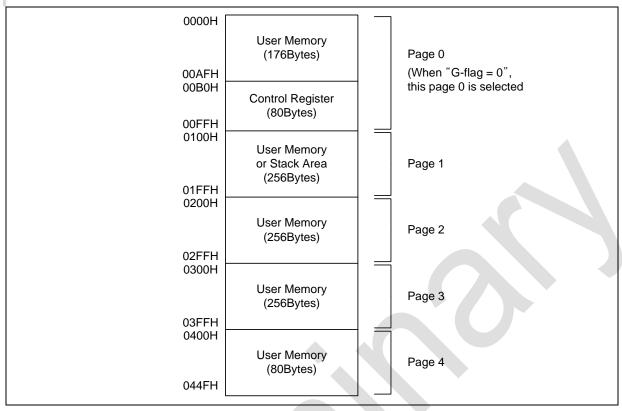

# 9.3 Data Memory

Figure 9-8 Data Memory Map

Figure 9-8 shows the internal Data Memory space available. Data Memory is divided into three groups, a user RAM, Stack memory and Control registers.

### 9.4 User Memory

The MC81F4x32 has a 512 bytes user memory (RAM). RAM pages are selected by the RPR register.

## **RPR**

#### RAM PAGE SELECT REGISTER

00E1H

|     | /   | О   | 5   | 4   | 3   |     | ı   | U      |              |

|-----|-----|-----|-----|-----|-----|-----|-----|--------|--------------|

| RPR |     |     |     | -   |     |     | RPF | R bits | Reset value: |

|     | R/W    | 00b          |

|          |                      | 000: page 0 | 011: page 3 |

|----------|----------------------|-------------|-------------|

| RPR bits | Ram Page Select bits | 001: page 1 | 100: page 4 |

|          |                      | 010: page 2 |             |

#### Note:

After setting RPR(RAM Page Select Register), be sure to execute SETG instruction. Whenever CLRG instruction is excuted, PAGE0 is selected regardless of RPR.

#### 9.5 Stack Area

The stack provides the area where the return address is saved before a jump is performed during the processing routine at the execution of a subroutine call instruction or the acceptance of an interrupt.

When returning from the processing routine, executing the subroutine return instruction [RET] restores the contents of the program counter from the stack; executing the interrupt return instruction [RETI] restores the contents of the program counter and flags.

The save/restore locations in the stack are determined by the stack pointed (SP). The SP is automatically decreased after the saving, and increased before the restoring. This means the value of the SP indicates the stack location number for the next save. Refer to Figure 9-4.

## 9.6 Control Registers (SFR)

The control registers are used by the CPU and Peripheral function blocks for controlling the desired operation of the device. Therefore these registers contain control and status bits for the interrupt system, the timer/ counters, analog to digital converters and I/O ports. The control registers are in address range of 0B0H to 0FFH. It also be called by SFR(Special Function Registers).

Note that unoccupied addresses may not be implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate effect.

More detailed information of each registers are explained in each peripheral section.

| E | xample : To write at CKCTLR       |

|---|-----------------------------------|

| L | DM CKCTLR,#0AH ;Divide ratio(÷32) |

|         | Pagister Name                               |        |     |   |   | In | itial | Val | ue |   |   | Addressing |

|---------|---------------------------------------------|--------|-----|---|---|----|-------|-----|----|---|---|------------|

| Address | Register Name                               | Symbol | R/W | 7 | 6 | 5  | 4     | 3   | 2  | 1 | 0 | Mode       |

| 00B0    | Timer 0 Status And Control Register         | T0SCR  | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

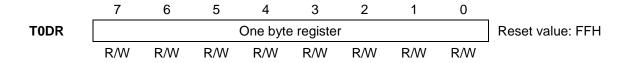

| 00B1    | Timer 0 Data Register                       | T0DR   | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

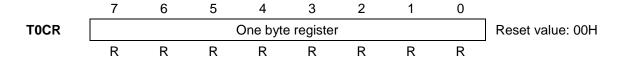

| 00B2    | Timer 0 Counter Register                    | T0CR   | R   | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00B3    | Timer 1 Status And Control Register         | T1SCR  | R/W | _ | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

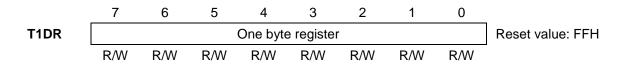

| 00B4    | Timer 1 Data Register                       | T1DR   | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

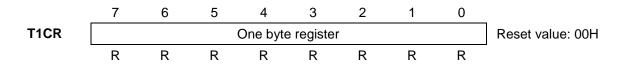

| 00B5    | Timer 1 Counter Register                    | T1CR   | R   | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00B6    | Timer 2 Status And Control Register         | T2SCR  | R/W | 0 | - | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

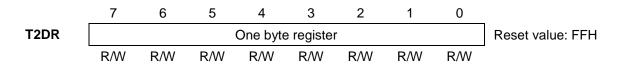

| 00B7    | Timer 2 Data Register                       | T2DR   | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

| 00B8    | Timer 2 Counter Register                    | T2CR   | R   | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00B9    | Timer 3 Status And Control Register         | T3SCR  | R/W | _ | _ | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

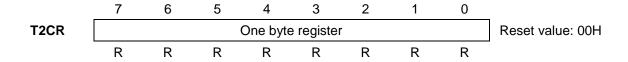

| 00BA    | Timer 3 Data Register                       | T3DR   | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

| 00BB    | Timer 3 Counter Register                    | T3CR   | R   | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00BC    | Oscillator Select Register                  | OSCSEL | R/W | _ | 7 | -  | 1     | -   | 0  | 0 | 0 | Byte, bit  |

| 00BD    | A/D Mode Register                           | ADMR   | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00BE    | A/D Converter Data High Register            | ADDRH  | R   | Χ | Χ | Χ  | X     | Χ   | Χ  | Χ | Χ | Byte, bit  |

| 00BF    | A/D Converter Data Low Register             | ADDRL  | R   | Χ | Х | Χ  | X     | ĺ   | 7  | - | _ | Byte, bit  |

| 00C0    | R0 Port Data Register                       | R0     | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00C1    | R1 Port Data Register                       | R1     | R/W | 1 | 1 | 1  | 1     | 1   | 0  | 0 | 0 | Byte, bit  |

| 00C2    | R2 Port Data Register                       | R2     | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

| 00C3    | R3 Port Data Register                       | R3     | R/W | _ | _ | 0  | 0     | 0   | 1  | 1 | 1 | Byte, bit  |

| 00C4    | R4 Port Data Register                       | R4     | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

| 00C5    | R5 Port Data Register                       | R5     | R/W | - | - | -  | -     | 1   | 1  | 1 | 1 | Byte, bit  |

| 00C6    | R0 Port Control High Register               | R0CONH | R/W | 0 | 0 | 0  | 0     | 0   | 0  | _ | 0 | Byte, bit  |

| 00C7    | R0 Port Control Middle Register             | R0CONM | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00C8    | R0 Port Control Low Register                | R0CONL | R/W | - | - | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00C9    | R0 Port Pull-up Enable Register             | PUR0   | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00CA    | R0 Port External Interrupt High Register    | EINT0H | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00CB    | R0 Port External Interrupt Low<br>Register  | EINT0L | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00CC    | R0 Port External Interrupt Request Register | ERQ0   | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00CD    | External Interrupt Flag Register            | EINTF  | R/W | 0 | 0 | 0  | 0     | 0   | 0  | 0 | 0 | Byte, bit  |

| 00CE    | PWM Status And Control Register             | PWMSCR | R/W | 0 | 0 | 0  | 0     | _   | _  | _ | _ | Byte, bit  |

| 00CF    | PWM Period And Duty Register                | PWMPDR | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

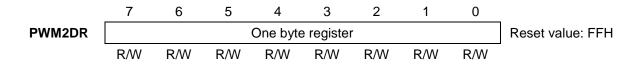

| 00D0    | PWM2 Data Register                          | PWM2DR | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

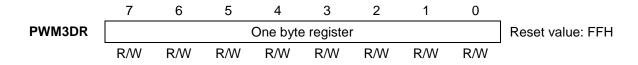

| 00D1    | PWM3 Data Register                          | PWM3DR | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |

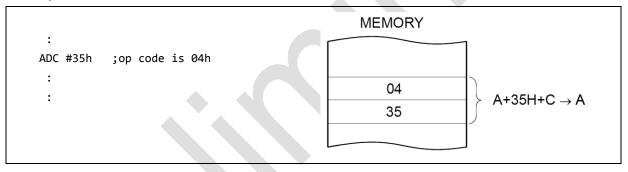

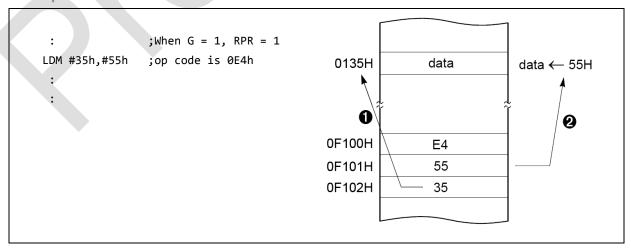

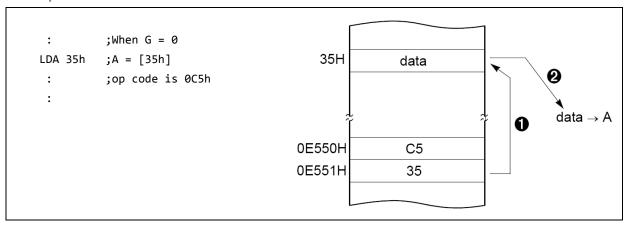

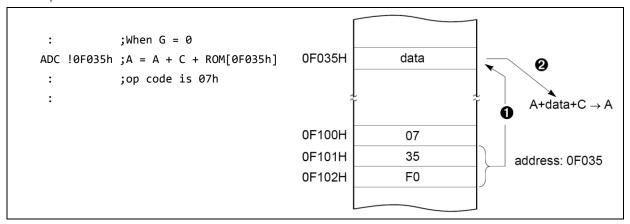

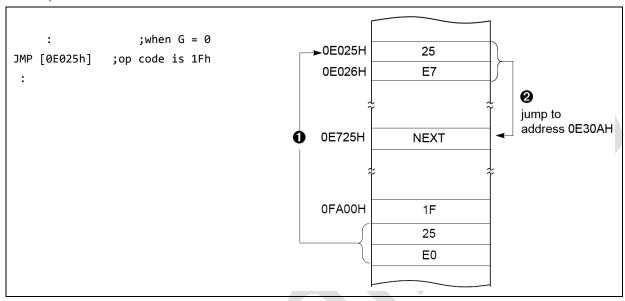

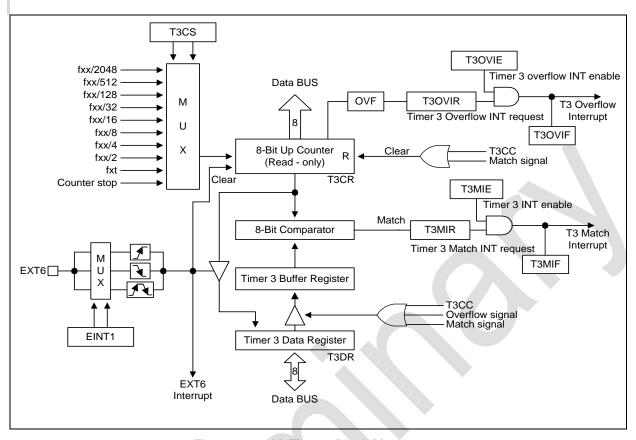

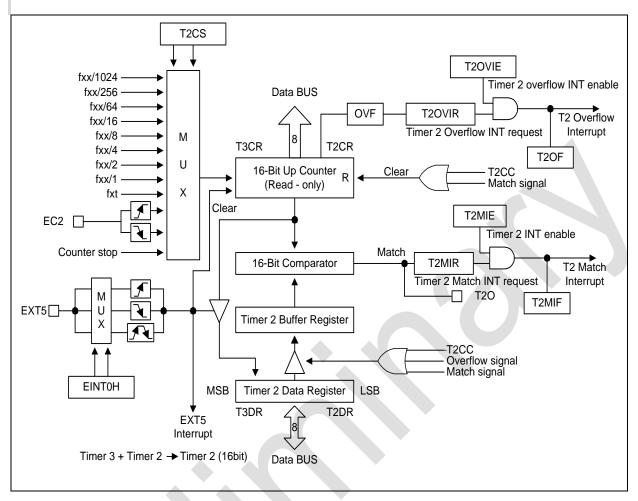

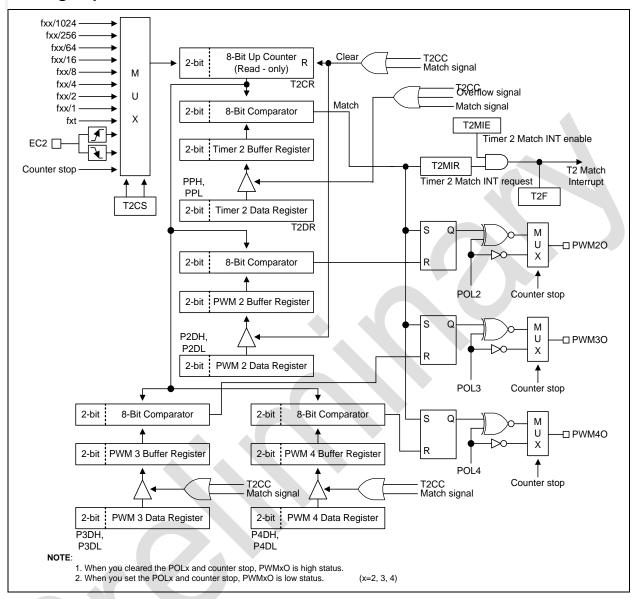

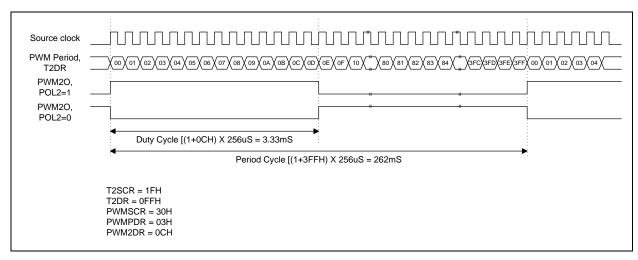

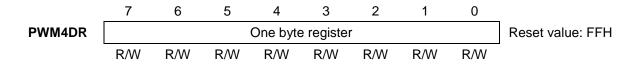

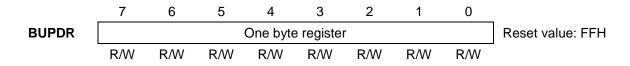

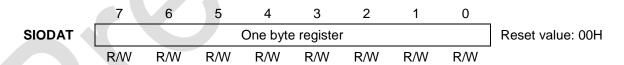

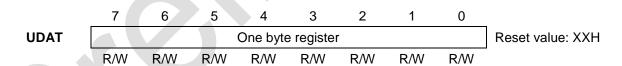

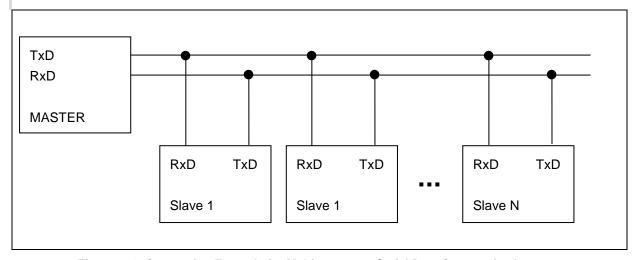

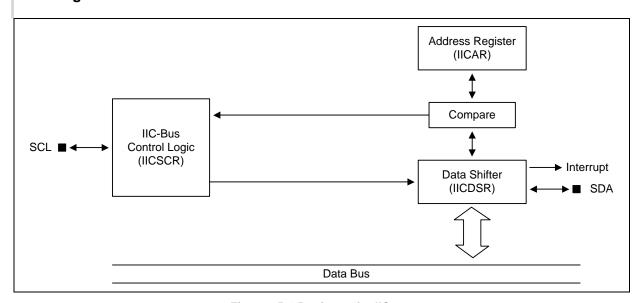

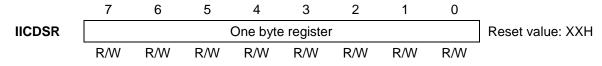

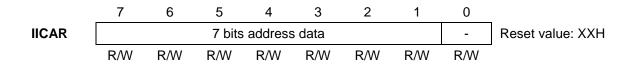

| 00D2    | PWM4 Data Register                          | PWM4DR | R/W | 1 | 1 | 1  | 1     | 1   | 1  | 1 | 1 | Byte, bit  |